ZHCABK1A February 2022 – March 2024 ADS1119 , ADS1120 , ADS1120-Q1 , ADS112C04 , ADS112U04 , ADS1130 , ADS1131 , ADS114S06 , ADS114S06B , ADS114S08 , ADS114S08B , ADS1158 , ADS1219 , ADS1220 , ADS122C04 , ADS122C14 , ADS122S14 , ADS122U04 , ADS1230 , ADS1231 , ADS1232 , ADS1234 , ADS1235 , ADS1235-Q1 , ADS124S06 , ADS124S08 , ADS1250 , ADS1251 , ADS1252 , ADS1253 , ADS1254 , ADS1255 , ADS1256 , ADS1257 , ADS1258 , ADS1258-EP , ADS1259 , ADS1259-Q1 , ADS125H01 , ADS125H02 , ADS1260 , ADS1260-Q1 , ADS1261 , ADS1261-Q1 , ADS1262 , ADS1263 , ADS127L01 , ADS130E08 , ADS131A02 , ADS131A04 , ADS131E04 , ADS131E06 , ADS131E08 , ADS131E08S , ADS131M02 , ADS131M03 , ADS131M04 , ADS131M06 , ADS131M08

- 1

- 摘要

- 商标

- 1电桥概述

- 2电桥结构

- 3电桥连接

- 4电桥测量的电气特性

- 5信号链设计注意事项

-

6电桥测量电路

- 6.1 使用比例基准和单极低电压 (≤ 5V) 激励源的四线电阻式电桥测量

- 6.2 使用比例基准和单极低电压 (≤ 5V) 激励源的六线电阻式电桥测量

- 6.3 使用伪比例基准和单极高电压 (> 5V) 激励源的四线电阻式电桥测量

- 6.4 使用伪比例基准和非对称高电压 (> 5V) 激励源的四线电阻式电桥测量

- 6.5 使用比例基准和电流激励的四线电阻式电桥测量

- 6.6 使用伪比例基准和单极低电压 (≤ 5V) 激励源,测量多个串联四线电阻式电桥

- 6.7 使用带比例基准和单极低电压 (≤ 5V) 激励源的单通道 ADC 测量多个并联的四线电阻式电桥

- 6.8 使用带比例基准和单极低电压 (≤ 5V) 激励源的多通道 ADC 测量多个并联的四线电阻式电桥

- 7总结

- 8Revision History

6.5.4 设计注意事项

IDAC 电流 IIDAC 与标称电桥电阻 RBRIDGE 一起确定电桥两端的总电压 VBRIDGE。假设导线电阻为零,则 VBRIDGE = VEXCITATION = VEXCITATION+ – VEXCITATION-,这也用作 ADC 基准电压 VREF。与节 6.1中所述的 VEXCITATION 固定不变的电路不同,VBRIDGE 会随着 RBRIDGE 变化而变化。这个不断变化的 VBRIDGE 电压也会导致 VREF 和 ADC 输入电压也发生变化。此外,电流源不会像在其他电桥测量电路中那样,使电桥共模电压 VCM(Bridge) 处于中间值。偏置电阻器 RBIAS 有助于使 VCM(Bridge) 保持在 ADC 模拟输入和电压基准输入的共模范围内。

RBRIDGE 由于拉伸或压缩产生的微小变化会导致差分电桥输出电压发生变化。PGA 集成到 ADC 中,并增益该低电平信号,从而降低系统噪声并提高 ADC 满量程范围 (FSR) 的利用率。ADC 对这个经过放大的电压进行采样并对照 VREF 进行转换,该电压与用于激励电桥的电压相同,因此是比例电压。在比例基准配置中,VIN 和 VREF 中的激励源噪声和漂移是相等的,从而有效地从 ADC 输出代码中消除了这些误差。

使用比例基准和电流激励的四线电阻式电桥测量需要:

- 差分模拟输入(AINP 和 AINN)

- 差分基准输入(REFP 和 REFN)

- 低噪声放大器

- 恒流源 (IDAC)

- 偏置电阻器(在某些情况下可选)

此外,使用比例基准和电流激励的四线电阻式电桥测量需要考虑多个因素,包括:

- 绝对(VREFP 和 VREFN)和差分 (VREF) 基准电压

- 电桥激励电流 IIDAC

- IDAC 顺从电压

- 电桥共模电压 VCM(Bridge)

- 电桥两端电压 VBRIDGE

- 电桥电阻 RBRIDGE

- 偏置电阻值 RBIAS

所有这些因素都相互关联,选择其中一个因素会影响其他一个或多个因素的选择。因此,可能需要进行多次设计迭代才能确定符合所有系统规格的最终结果。

为了减少可能的电路配置次数,建议开始设计时选择具有差分 VREF 输入、集成式 IDAC 和 PGA 的 ADC 。绝对和差分 VREF 规格约束 VBRIDGE 的可能值。集成式 IDAC 将 IIDAC 的选择限制为几个离散值,不再需要使用外部电路来驱动电桥。集成式 IDAC 还有明确定义的顺从电压,可帮助确定 RBRIDGE 和 RBIAS 的最大值。集成 PGA 通常需要模拟电源电压一半 (AVDD/2) 的共模电压,从而尽可能提高放大器增益,并将 PGA 输出电压保持在线性工作范围内。这会将目标 VCM(Bridge) 设置为 AVDD/2,从而帮助确定是否需要 RBIAS 电阻,如果需要,将会确定所需的电阻值。

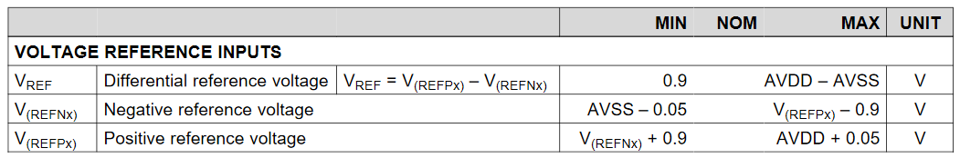

例如,24 位 ADS1261 集成了所有这些必要特性。图 6-8 显示了 ADS1261 的差分和绝对 VREF 电压要求。在使用单极电源以使 AVDD = 5V 且 AVSS = 0V 的情况下,图 6-8 显示了 VREF 必须介于 0.9V 和 5V 之间。这会界定 VBRIDGE 的可能值。此外,VREFN 上的绝对电压可以向下扩展到 AVSS,而 VREFP 上的绝对电压可以向上扩展到 AVDD。这种较宽的绝对 VREF 电压范围通常不会限制其他系统元件的选择,但这一点应始终在每个设计中加以验证。

图 6-8 ADS1261 VREF 工作条件

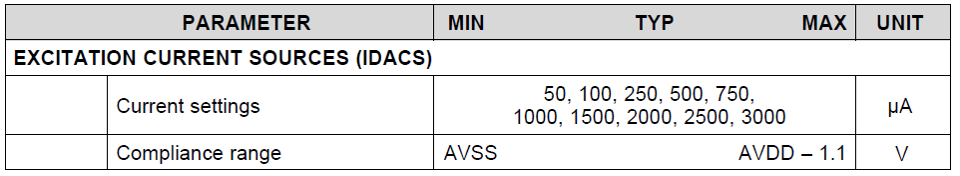

图 6-8 ADS1261 VREF 工作条件图 6-9 显示了 ADS1261 的可用 IDAC 电流设置和顺从电压。集成到精密 ADC 中的 IDAC 需要一定的 AVDD 余量以保持电流大小。由于 ADS1261 的 AVDD = 5V ±5%,IDAC 顺从电压 = AVDD – 1.1V = 3.9V。此值设置 RBRIDGE + RBIAS 以及 IIDAC 上的上限。

图 6-9 ADS1261 IDAC 电流设置和顺从电压

图 6-9 ADS1261 IDAC 电流设置和顺从电压为了确定 VCM(Bridge) 是否处于 PGA 线性运行区域内,节 6.3.4介绍了 ADS1261 Excel 计算器,该计算器可绘制 PGA 输出曲线以展示输入参数是否有效。还可以选择所需的目标值,例如 VCM(Bridge) = AVDD/2,然后围绕这个共模电压设计系统的其余部分。定义了具体的 ADC 工作条件后,开始选择其余的系统元件值。

对于本示例,假设 RBRIDGE 可以是以下四个常用电桥电阻值中的任何一个值:120Ω、350Ω、1kΩ 或 3.5kΩ。然后,使用图 6-9 中给出的 ADS1261 IDAC 值,按照表 6-19 中的公式确定 VBRIDGE。表 6-12 计算 IIDAC 和 RBRIDGE 所有可能组合下的 VBRIDGE。

RBRIDGE (Ω) | IIDAC (μA) | |||||||||

50 | 100 | 250 | 500 | 750 | 1000 | 1500 | 2000 | 2500 | 3000 | |

120 | 0.006 | 0.012 | 0.030 | 0.060 | 0.090 | 0.120 | 0.180 | 0.240 | 0.300 | 0.360 |

350 | 0.018 | 0.035 | 0.088 | 0.175 | 0.263 | 0.350 | 0.525 | 0.700 | 0.875 | 1.050 |

1000 | 0.050 | 0.100 | 0.250 | 0.500 | 0.750 | 1.000 | 1.500 | 2.000 | 2.500 | 3.000 |

3500 | 0.175 | 0.350 | 0.875 | 1.750 | 2.625 | 3.500 | 5.250 | 7.000 | 8.750 | 10.500 |

假设没有导线电阻,则 VBRIDGE = VREF。因此,表 6-12 根据 ADS1261 的要求,还用绿色突出显示了 0.9V < VBRIDGE < 5V 下所有可能的系统组合。在 40 种可能的组合中,只剩下9种。

接下来,通过为 VCM(Bridge) 选择一个值,确定剩余九种组合中每种组合的 RBIAS 可能值。本示例使用 VCM(Bridge) = AVDD/2,但也可以使用其他电压。始终确保,对于目标增益值,要满足 PGA 共模和绝对电压的要求。

按照表 6-19,VCM(Bridge) = VBRIDGE / 2 + VBIAS,VBRIDGE = IIDAC • RBRIDGE,VBIAS = IIDAC • RBIAS。重新排列这些公式,可确定用 IIDAC、RBRIDGE 和 AVDD 表示的 RBIAS,如方程式 60 所示:

关于方程式 60 的一个重要细节是,RBIAS 可以为 0Ω,从而将 VCM(Bridge) 公式简化为 VCM(Bridge) = VBRIDGE / 2。也就是说,只要仍然可以满足 ADC 和系统要求,就可以消除 RBIAS 电阻。但本示例假设 RBIAS 电阻是必需的。在任一种情况下,下一步是使用表 6-19 中的公式计算 VCOMPLIANCE。表 6-13 提供了表 6-12 中九种有效组合中每种组合的 RBIAS 和 VCOMPLIANCE 计算值。此外,表 6-13 以绿色突出显示了处于 ADS1261 IDAC 顺从电压 3.9V 范围的 VCOMPLIANCE 值。

| RBRIDGE (Ω) | IIDAC (μA) | RBIAS (Ω) | VCOMPLIANCE (V) |

|---|---|---|---|

| 350 | 3000 | 658 | 3.025 |

| 1000 | 1000 | 2000 | 3.000 |

| 1500 | 1167 | 3.250 | |

| 2000 | 750 | 3.500 | |

| 2500 | 500 | 3.750 | |

| 3000 | 333 | 4.000 | |

| 3500 | 500 | 3250 | 3.375 |

| 750 | 1583 | 3.813 | |

| 1000 | 750 | 4.250 |

如表 6-13 所示,原始九种组合中的七种组合处于 ADS1261 指定的 IDAC 3.9V 顺从电压范围内。最终设计中可以使用上述任何选项。例如,图 6-10 显示了 RBRIDGE = 1kΩ、RBIAS = 2kΩ、IIDAC = 1mA 的系统。IDAC 电流路径以红色突出显示,得到的系统电压以蓝色突出显示。

图 6-10 使用 RBRIDGE = 1kΩ、RBIAS = 2kΩ 和 IIDAC = 1mA 进行的电流激励电桥测量

图 6-10 使用 RBRIDGE = 1kΩ、RBIAS = 2kΩ 和 IIDAC = 1mA 进行的电流激励电桥测量图 6-10 中有一个以前未讨论过的重要结果,是 VBRIDGE = VREF = 1V。也就是说,电流激励系统的 VEXCITATION 等于 1V,而电压激励系统的 VEXCITATION 通常大于等于 5V。假设每个电桥具有相同的灵敏度,电流激励电桥的输出电压是电压激励电桥的 20%。考虑到系统噪声目标,这可以将系统的动态范围降低到不可接受的水平。在这种情况下,应使用不同的 ADC、分立式电流源或更宽范围的 RBRIDGE 值重复该设计过程。

选择了系统配置后,使用表 6-19 中的公式和表 6-18 中的参数,确定电桥的最大差分输出电压 VOUT(Bridge Max)。该值是电桥在正常工作条件下可以提供的最大输出电压,并对应于可以施加到电桥的最大负载 Load(Bridge Max)。如果系统不使用电桥的整个输出范围,则 VOUT(System Max) 定义的是施加到特定系统的最大差分输出信号,Load(System Max) 是对应的最大负载。例如,如果 VOUT(Bridge Max) 对应于 Load(Bridge Max) = 5kg,但系统规格只要求 Load(System Max) = 2.5kg,则 VOUT(System Max) 由方程式 61 给出:

请注意,如果 Load(System Max) = Load(Bridge Max),则 VOUT(System Max) = VOUT(Bridge Max)。

确定了 VOUT(System Max) 后,要为 ADC PGA 选择对应的增益值。最大增益值受之前所选的 VCM(Bridge) 值和 ADC FSR 限制。鉴于VCM(Bridge) 电压小于 ADC FSR,放大器增益应该是 使 PGA 输出电压保持在线性工作范围 的最大允许值。在某些情况下,无法选择使用整个 ADC FSR 的放大器增益。虽然这通常是分辨率和易用性之间的一种可接受的折衷,但应确保在 ADC FSR 无法最大化的情况下仍然满足所有系统要求。

最后,如果需要校准,请按照节 5.5中的说明操作。