ZHCSR35A November 2019 – August 2020 BQ79600-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 规格

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Functional Modes and Power Supply

- 7.3.2 Communication

- 7.3.3 Fault Handling

- 7.3.4 INH/ Reverse Wakeup

- 7.3.5 Sniff Detector

- 7.3.6 Device Diagnostic

- 7.4 Device Functional Modes

- 7.5

Register Maps

- 7.5.1 Register Summary Table

- 7.5.2 Register: DIR0_ADDR

- 7.5.3 Register: DIR1_ADDR

- 7.5.4 Register: CONTROL1

- 7.5.5 Register: CONTROL2

- 7.5.6 Register: DIAG_CTRL

- 7.5.7 Register: DEV_CONF1

- 7.5.8 Register: DEV_CONF2

- 7.5.9 Register: TX_HOLD_OFF

- 7.5.10 Register: SLP_TIMEOUT

- 7.5.11 Register: COMM_TIMEOUT

- 7.5.12 Register: SPI_FIFO_UNLOCK

- 7.5.13 Register: FAULT_MSK

- 7.5.14 Register: FAULT_RST

- 7.5.15 Register: FAULT_SUMMARY

- 7.5.16 Register: FAULT_REG

- 7.5.17 Register: FAULT_SYS

- 7.5.18 Register: FAULT_PWR

- 7.5.19 Register: FAULT_COMM1

- 7.5.20 Register: FAULT_COMM2

- 7.5.21 Register: DEV_DIAG_STAT

- 7.5.22 Register: PARTID

- 7.5.23 Register: DIE_ID1

- 7.5.24 Register: DIE_ID2

- 7.5.25 Register: DIE_ID3

- 7.5.26 Register: DIE_ID4

- 7.5.27 Register: DIE_ID5

- 7.5.28 Register: DIE_ID6

- 7.5.29 Register: DIE_ID7

- 7.5.30 Register: DIE_ID8

- 7.5.31 Register: DIE_ID9

- 7.5.32 Register: DEBUG_CTRL_UNLOCK

- 7.5.33 Register: DEBUG_COMM_CTRL

- 7.5.34 Register: DEBUG_COMM_STAT

- 7.5.35 Register: DEBUG_SPI_PHY

- 7.5.36 Register: DEBUG_SPI_FRAME

- 7.5.37 Register: DEBUG_UART_FRAME

- 7.5.38 Register: DEBUG_COMH_PHY

- 7.5.39 Register: DEBUG_COMH_FRAME

- 7.5.40 Register: DEBUG_COML_PHY

- 7.5.41 Register: DEBUG_COML_FRAME

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

7.3.2.1.1.1 Calculating Frame CRC Value

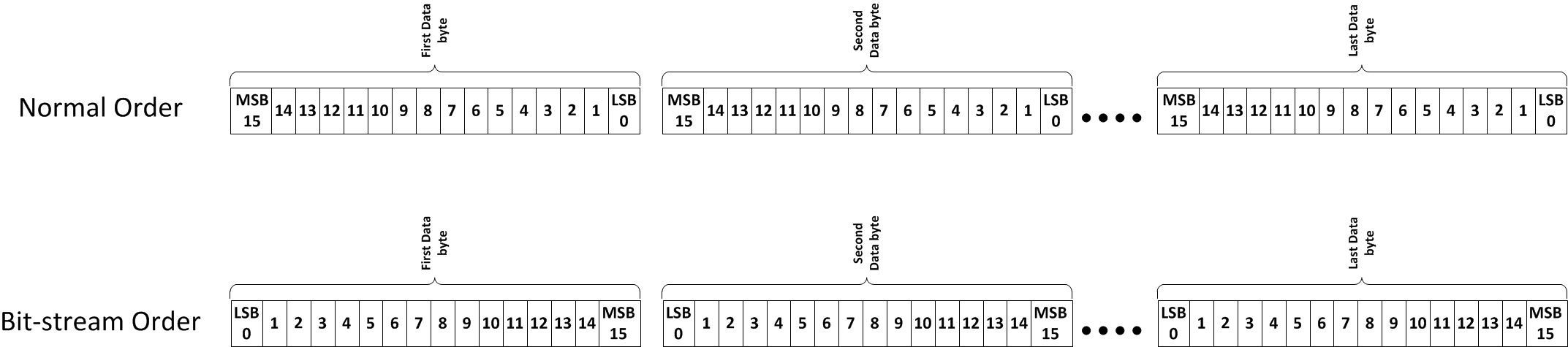

The CRC calculation by the transmitter is in bit-stream order across the entire transmission frame (except for the CRC). When determining bit-stream order for implementing the CRC algorithm, it is important to note that protocol bytes transmit serially, least-significant bit first. Figure 7-9 illustrates the bit-stream order concept.

Figure 7-9 Bit-Stream Order Explanation

Figure 7-9 Bit-Stream Order ExplanationThe CRC (0x0000) is appended to the end of the bit-stream. This bit-stream is then initialized by XOR'ing with 0xFFFF to catch any leading 0 errors. This new bit-stream is then divided by the polynomial (0xC002) until only the 2-byte CRC remains. During this process, the most significant 17 bits of the bit stream are XOR’d with the polynomial. The leading zeroes of the result are removed and that result is XOR’d with the polynomial once again. The process is repeated until only the 2-byte CRC remains. For example:

Example 1: CRC Calculation Using Polynomial Division

Command Frame = 0x80 00 02 0F 0B (0b1000 0000 0000 0000 0000 0010 0000 1111 0000 1011)

Command Frame in bit stream order = 0x01 00 40 F0 D0 (0b0000 0001 0000 0000 0100 0000 1111 0000 1101 0000)

After Initialization (XOR with 0xFFFF) = 0b1111 1110 1111 1111 0100 0000 1111 0000 1101 0000

1111 1110 1111 1111 0100 0000 1111 0000 1101 0000 0000 0000 0000 0000 #append 0x0000 for CRC

1100 0000 0000 0010 1 #XOR with polynomial

0011 1110 1111 1101 1100 0000 1111 0000 1101 0000 0000 0000 0000 0000

11 1110 1111 1101 1100 0000 1111 0000 1101 0000 0000 0000 0000 0000 #delete leading zeros from previous result

11 0000 0000 0000 101 #XOR with polynomial

00 1110 1111 1101 0110 0000 1111 0000 1101 0000

……

……

……

1100 0110 0000 0001 0000 0000

1100 0000 0000 0010 1 #XOR with polynomial

0000 0110 0000 0011 1000 0000

110 0000 0011 1000 0000

110 0000 0000 0001 01 #XOR with polynomial

000 0000 0011 1001 0100

0000 0011 1001 0100 #CRC result in bit stream order

1100 0000 0010 1001 #final CRC result in normal order

CRC final 0xC029