ZHCU712B april 2020 – july 2023

- 1

- CLB 工具

- 商标

- 1引言

- 2开始使用

- 3使用 CLB 工具

-

4示例

- 4.1 基础示例

- 4.2

入门示例

- 4.2.1 示例 1 – 组合逻辑

- 4.2.2 示例 2 – GPIO 输入滤波器

- 4.2.3 示例 4 – PWM 保护

- 4.2.4 示例 5 – 事件窗口

- 4.2.5 示例 6 – 信号生成和检查

- 4.2.6 示例 8 – 外部与门

- 4.2.7 示例 9 – 计时器

- 4.2.8 示例 10 – 具有两种状态的计时器

- 4.2.9 示例 11 – 中断标签

- 4.2.10 示例 12 – 输出相交

- 4.2.11 示例 17 - 单次 PWM 生成

- 4.2.12 示例 21 - 时钟预分频器和 NMI

- 4.2.13 示例 22 - 串行器

- 4.2.14 示例 23 - LFSR

- 4.2.15 示例 24 - 锁定输出屏蔽

- 4.2.16 示例 25 - 输入流水线模式

- 4.2.17 示例 26 - 计时流水线模式

- 4.3 专家示例

- 5在现有 DriverLib 工程中启用 CLB 工具

- 6常见问题解答 (FAQ)

- 7修订历史记录

3.5.3 运行仿真

定义 CLB 配置和输入激励之后,用户可以编译工程。下面概述了生成“CLB.vcd”的完整步骤。

- 启用 Tile Design 模块顶部的“Global Parameters”下拉列表中的“Generate CLB Simulation File”复选框。

- 构建工程以验证 Tile Design 设置是否正确无误

- 在文件浏览器或命令行中,执行“clb_simulation”文件。此文件位于保存生成的 SysConfig 文件的位置。对于 CCS,这是工程构建配置目录中的 syscfg 目录(例如“CPU1_RAM/syscfg”)

- 打开“simulation”目录(位于执行“clb_simulation”的目录上层)

- 双击“CLB.vcd”文件

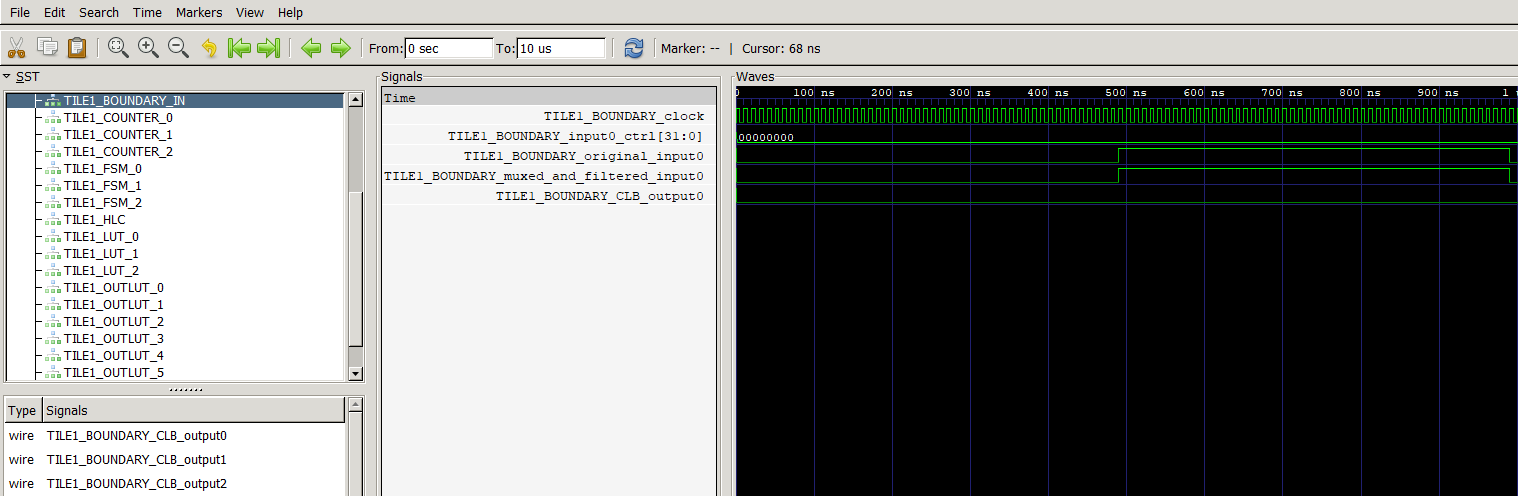

假设已经完成了波形查看器配置,双击“CLB.vcd”文件应打开查看器并允许检查波形。图 3-20 显示了设置为显示输入波形样本的 GTKWave 查看器。有关如何添加和查看信号的信息,请参阅查看器文档。

图 3-20 CLB 仿真示例

图 3-20 CLB 仿真示例如果仿真波形与期望的波形不相符,请修改 .syscfg 文件中的配置并重复仿真。