ZHCU712B april 2020 – july 2023

- 1

- CLB 工具

- 商标

- 1引言

- 2开始使用

- 3使用 CLB 工具

-

4示例

- 4.1 基础示例

- 4.2

入门示例

- 4.2.1 示例 1 – 组合逻辑

- 4.2.2 示例 2 – GPIO 输入滤波器

- 4.2.3 示例 4 – PWM 保护

- 4.2.4 示例 5 – 事件窗口

- 4.2.5 示例 6 – 信号生成和检查

- 4.2.6 示例 8 – 外部与门

- 4.2.7 示例 9 – 计时器

- 4.2.8 示例 10 – 具有两种状态的计时器

- 4.2.9 示例 11 – 中断标签

- 4.2.10 示例 12 – 输出相交

- 4.2.11 示例 17 - 单次 PWM 生成

- 4.2.12 示例 21 - 时钟预分频器和 NMI

- 4.2.13 示例 22 - 串行器

- 4.2.14 示例 23 - LFSR

- 4.2.15 示例 24 - 锁定输出屏蔽

- 4.2.16 示例 25 - 输入流水线模式

- 4.2.17 示例 26 - 计时流水线模式

- 4.3 专家示例

- 5在现有 DriverLib 工程中启用 CLB 工具

- 6常见问题解答 (FAQ)

- 7修订历史记录

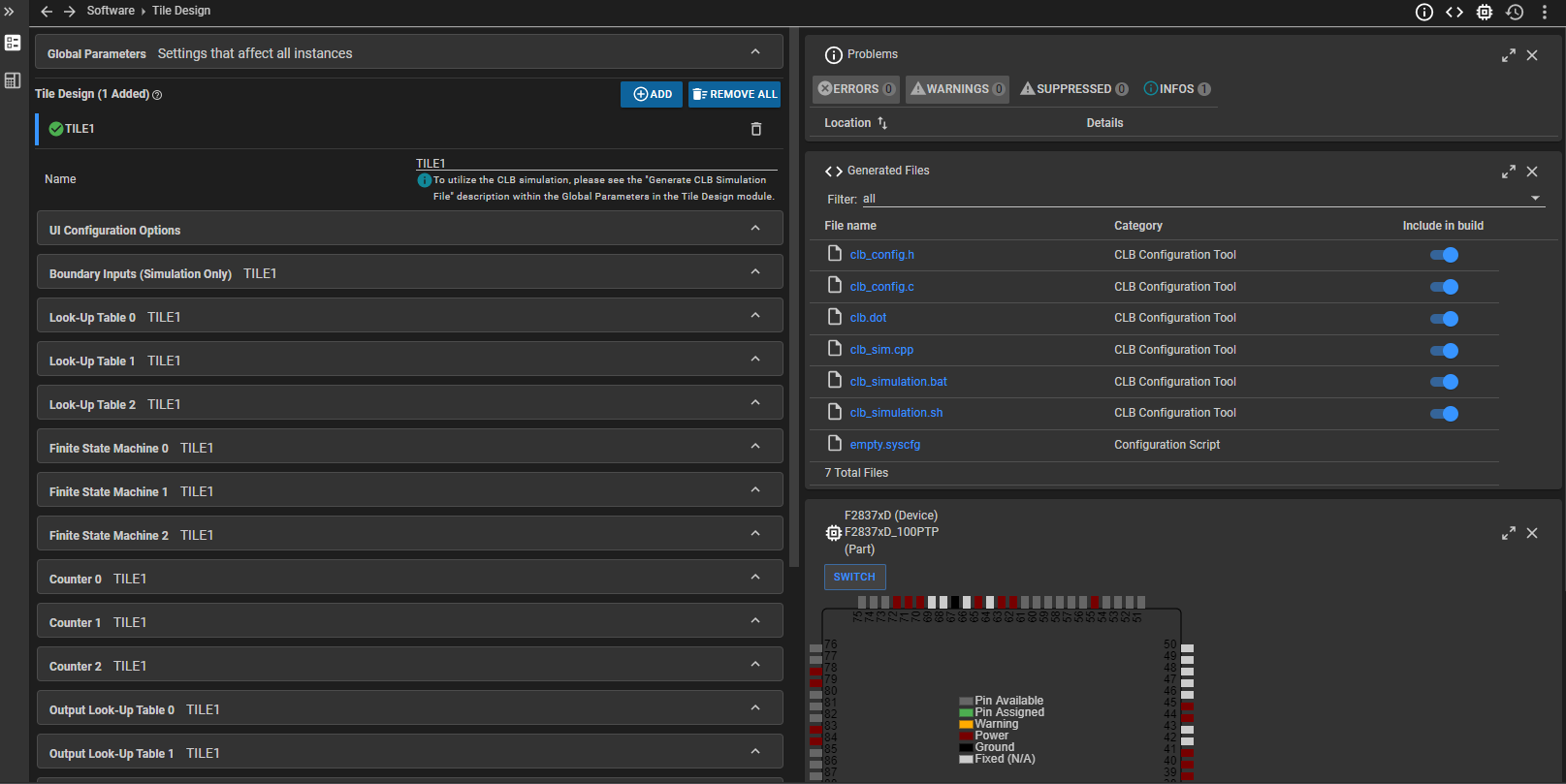

3.3 配置 CLB 逻辑块

要打开 SysConfig 工具,请在 CCS Project Explorer 窗口中双击您要编辑的“.syscfg”文件。图 3-5 显示了相关屏幕。

图 3-5 CLB 工具 SysConfig 屏幕

图 3-5 CLB 工具 SysConfig 屏幕如果未打开该屏幕,请确保您已正确完成之前的步骤。

每个 .syscfg 文件中都包含 CLB 逻辑块的配置。您可以根据需要更改逻辑块的名称。对于突出显示的逻辑块,在右侧窗格中显示了子模块列表。通过选择子模块,可以检查和编辑每个子系统的参数。

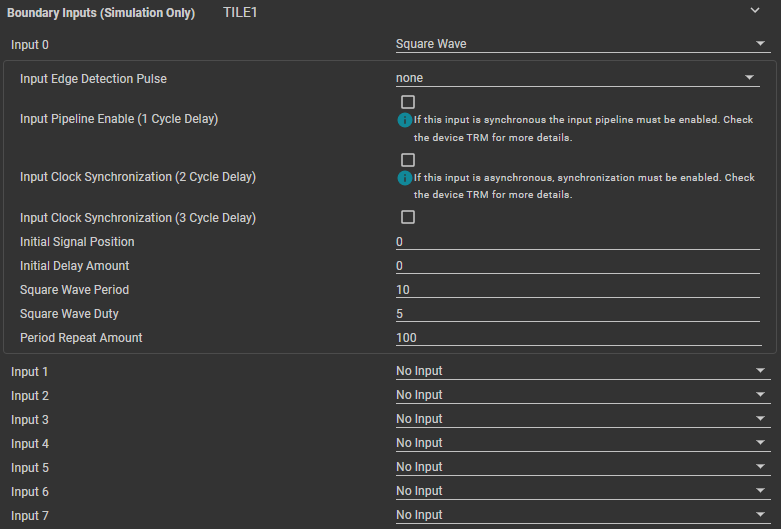

“BOUNDARY”项目是一种特殊情况。该组允许用户选择仅用于仿真的逻辑块输入。生成工具配置时,CLB 输入始终来自 SysConfig 中的 CLB 模块,不过,出于仿真目的,用户可以指定方波信号源、周期和占空比(均以时钟周期为单位)、同步以及输入流水线条件,如图 3-6 中所示。还支持用于仿真目的的自定义波形生成。有关仿真器的更多信息,请参阅节 3.5。这些选项仅用于仿真,不会影响实际的 CLB 配置或其在器件上的实现。

图 3-6 边界输入选项

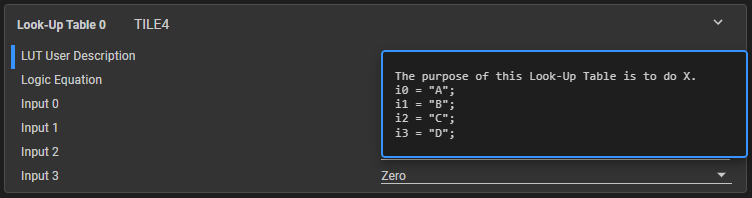

图 3-6 边界输入选项用户使用工具中的复选框和下拉选项配置和连接每个逻辑块中的子模块。除“BOUNDARY”外的所有子模块也都有“User Description”。此说明是一个多行文本框,用户可以在其中输入注释以帮助提供 CLB 每个部分的上下文。

图 3-7 “User Description”文本框

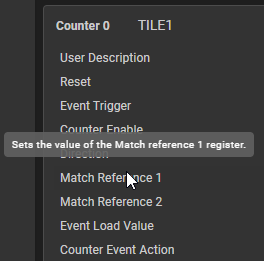

图 3-7 “User Description”文本框当鼠标光标悬停在配置工具中的每个项目上时,会显示上下文相关帮助。图 3-8 显示了“Counter 0”子模块中“Match Reference 1”字段的示例。

图 3-8 计数器选项

图 3-8 计数器选项通过使用 C 格式的文本输入来配置 LUT 和 FSM 的逻辑方程。表 3-2 显示了布尔方程中允许使用的符号。

| 逻辑运算 | 符号 |

|---|---|

| 与 | & |

| 或 | | |

| 异或 | ^ |

| 非 | ! |

支持使用括号:例如,用户可以编写 i1 | !(i2 & i3)。输入方程后,该工具会对方程进行语法检查。无效的方程通过输入行下方的错误消息指示。

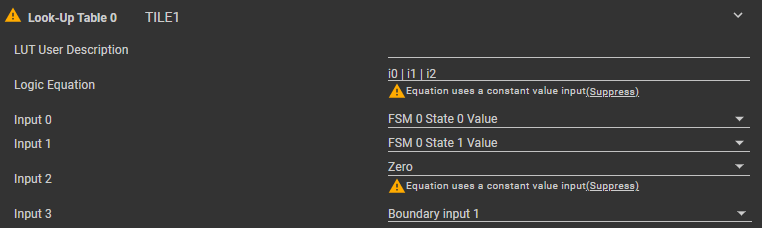

一些不太可能的逻辑组合会向用户生成警告。图 3-9 显示了一个示例,其中用户尝试在布尔方程的“LUT 0”中使用 i2 输入。但是,i2 被配置为一个常数,不太符合用户期望。该警告同时显示在方程下方和输入选择下方。

图 3-9 方程警告

图 3-9 方程警告对于某些字段,该工具会对数字输入执行范围检查,以确保它们落在允许的范围内。例如,尝试加载大于 232 的值的计数器子模块将产生警告,因为计数器只有 32 位宽。

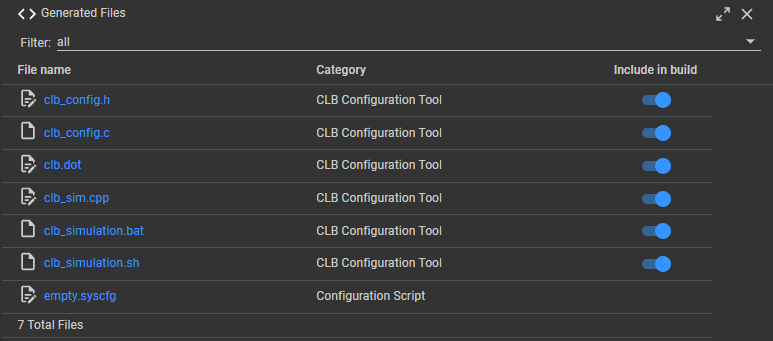

当用户输入配置数据时,该工具会自动生成若干个文件。要查看生成的文件,请点击该工具右上角的“< >”符号,然后选择文件名以打开它。

图 3-10 CLB 工具生成的文件

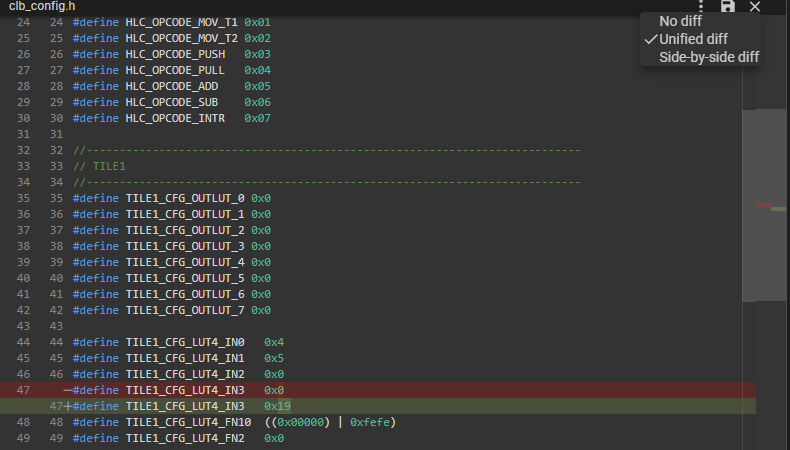

图 3-10 CLB 工具生成的文件CLB 寄存器设置包含在头文件“clb_config.h”中,用户可以通过点击文件名来打开该文件。图 3-11显示了一个示例。请务必记住,每次用户更改任何 CLB Tile Design 设置时,该工具都会更新此文件。因此,该工具将覆盖对所生成文件内容的手动更改。如果在更改 CLB 设置时该文件保持打开状态,则在选择“Unified Diff”选项时可以查看文件中受影响的寄存器数据的变化。

图 3-11 “clb.h”头文件示例

图 3-11 “clb.h”头文件示例利用文件“clb.dot”,用户可以检查子模块互连的外观。此方框图的 HTML 和 SVG 版本在编译后处理步骤中生成,可在 CCS 中打开和查看这些步骤。

图 3-12 CLB 方框图

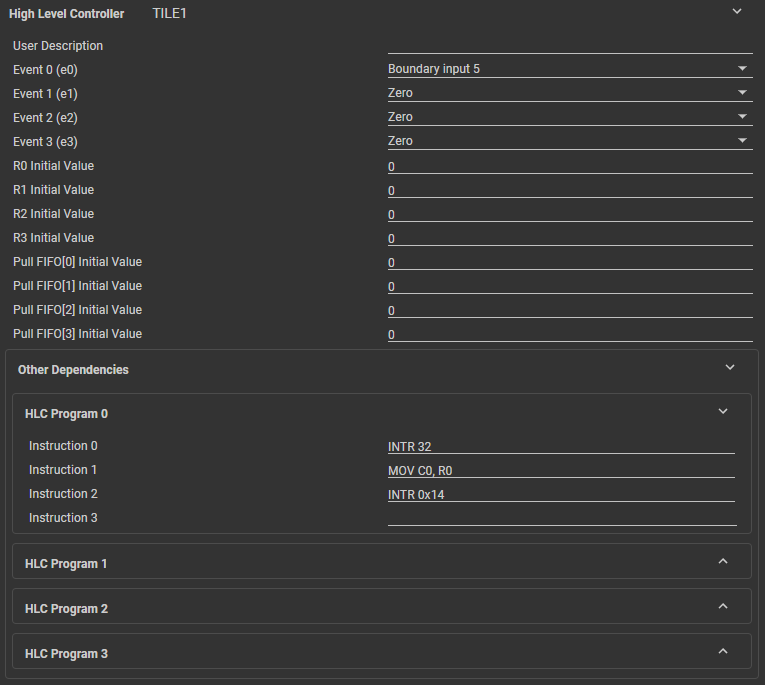

图 3-12 CLB 方框图HLC 子模块的字段包含用于配置事件和初始值的字段。四个事件中的每个事件都可能触发由最多八条指令构成的简短程序的执行。有关 HLC 的更多信息,请参阅器件特定 TRM。

可在“Other Dependencies”的“HLC Program”下拉列表中输入 HLC 指令。在使用完全部八条指令之前,会始终显示一个空白行。在图 3-13 中,用户选择了一个 HLC 触发事件并键入了一个由三条指令构成的简短程序。

图 3-13 HLC 配置示例

图 3-13 HLC 配置示例