ZHCU712B april 2020 – july 2023

- 1

- CLB 工具

- 商标

- 1引言

- 2开始使用

- 3使用 CLB 工具

-

4示例

- 4.1 基础示例

- 4.2

入门示例

- 4.2.1 示例 1 – 组合逻辑

- 4.2.2 示例 2 – GPIO 输入滤波器

- 4.2.3 示例 4 – PWM 保护

- 4.2.4 示例 5 – 事件窗口

- 4.2.5 示例 6 – 信号生成和检查

- 4.2.6 示例 8 – 外部与门

- 4.2.7 示例 9 – 计时器

- 4.2.8 示例 10 – 具有两种状态的计时器

- 4.2.9 示例 11 – 中断标签

- 4.2.10 示例 12 – 输出相交

- 4.2.11 示例 17 - 单次 PWM 生成

- 4.2.12 示例 21 - 时钟预分频器和 NMI

- 4.2.13 示例 22 - 串行器

- 4.2.14 示例 23 - LFSR

- 4.2.15 示例 24 - 锁定输出屏蔽

- 4.2.16 示例 25 - 输入流水线模式

- 4.2.17 示例 26 - 计时流水线模式

- 4.3 专家示例

- 5在现有 DriverLib 工程中启用 CLB 工具

- 6常见问题解答 (FAQ)

- 7修订历史记录

3.5.2 创建输入激励

通过在 CCS Project Explorer 窗口中双击文件名来打开 .syscfg 文件。选中“Boundary”类别,将其展开。

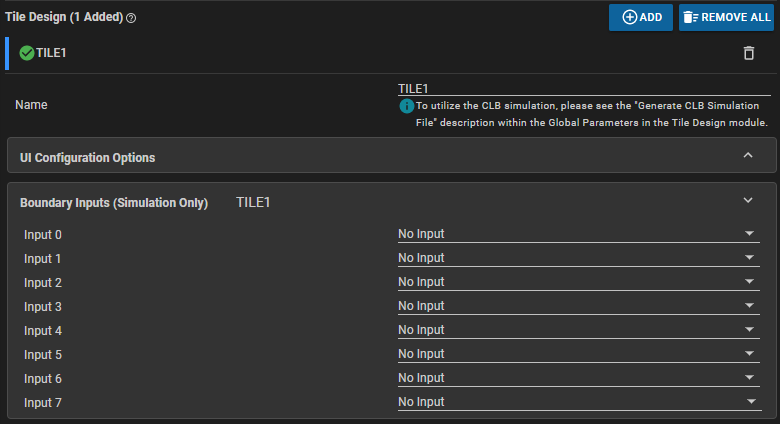

图 3-16 边界输入 0 到 7

图 3-16 边界输入 0 到 7可以使用下拉菜单为八个 CLB 输入中的每一个定义单独的输入激励。点击右侧的向下箭头可显示选项:

- No Input – 默认选项,不生成激励。

- Square Wave – 通过可配置初始信号位置、初始延迟、周期、占空比和周期重复量定义周期性 PWM 输入。

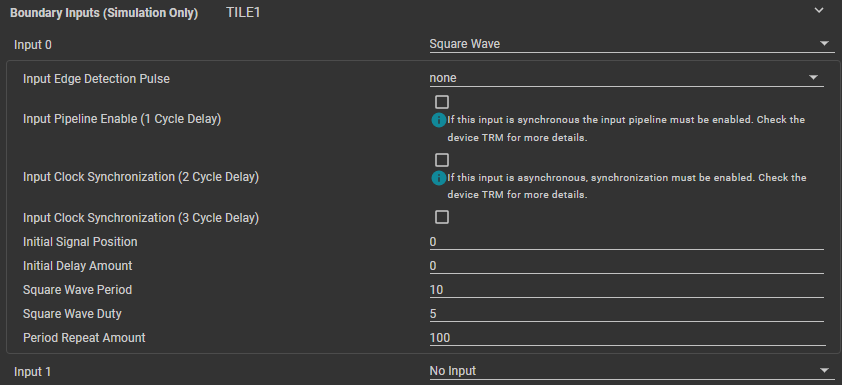

图 3-17 边界输入“Square Wave”

图 3-17 边界输入“Square Wave”“Input Edge Detection Pulse”选项为用户提供了通过 PWM 波的上升沿和/或下降沿生成脉冲的选择,在图 3-17 中,其周期和占空比分别设置为 10 个和 5 个 CLB 时钟脉冲。

“Input Pipeline Enable”复选框会向输入信号增加一个单周期延迟;输入信号用作路由到 CLB 作为输入的同步信号。请注意,流水线滤波器仅在某些 CLB 类型上可用。有关更多详细信息,请参阅器件特定 TRM 中的“CLB 输入多路复用器”部分。

“Input Clock Synchronization”复选框会强制输入波形与 CLB 时钟同步(同步器会产生 2-3 个周期的延迟,因此两个时序都有相应的复选框,因为无法预测确切的延迟)。对于来自相对于 CLB 的异步源的信号,此选项是必需的。有关更多信息,请参阅器件特定 TRM 中的“CLB 输入多路复用器”部分。

- Low (0) 或 High (1) - 分别将激励设置为恒定的低电平或高电平。

- Custom Wave Input - 使用伪代码生成自定义激励。

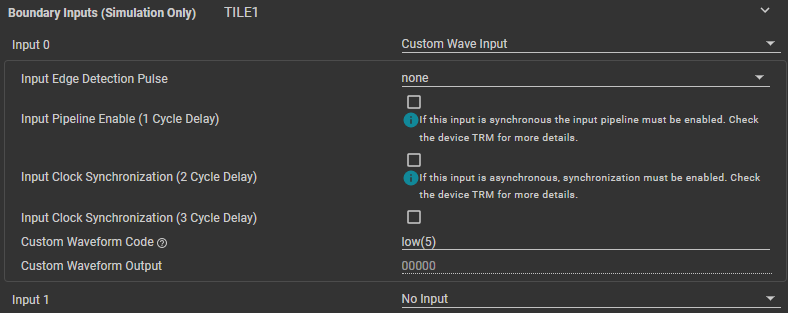

图 3-18 边界输入定制

图 3-18 边界输入定制“Input Edge Detection Pulse”、“Input Pipeline Enable”和“Input Clock Synchronization”与 Square Wave 激励的工作方式相同,但增加了定制波形伪代码。“high”、“low”和“rpt”指令的数值参数可以是十六进制 (0x1A) 或十进制 (26)。

表 3-2 定制波形代码指令指令 说明 #define 用于定义宏的模式替换器 high(N) 将“N”个 CLB 周期的波形设置为高电平 low(N) 将“N”个 CLB 周期的波形设置为低电平 rpt(N) 启动重复块;用 rpt(N) 和 rpt_end 封装的代码将一共重复“N”次 rpt_end 表示重复块结束 - Tile Output - 使用选定的逻辑块输出作为当前逻辑块的输入激励。

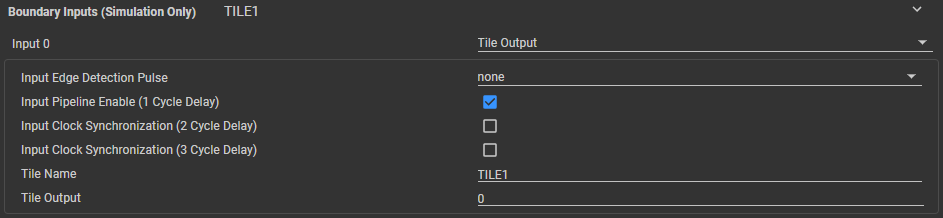

图 3-19 边界输入“Tile Output”

图 3-19 边界输入“Tile Output” - “Tile Name”必须是 CLB 工具工程中有效逻辑块的名称。由于 CLB 逻辑块的输出是同步的,因此应启用“Input Pipeline Enable”。有关更多信息,请参阅器件特定 TRM 中的 CLB 输入多路复用器 部分。