ZHCU712B april 2020 – july 2023

- 1

- CLB 工具

- 商标

- 1引言

- 2开始使用

- 3使用 CLB 工具

-

4示例

- 4.1 基础示例

- 4.2

入门示例

- 4.2.1 示例 1 – 组合逻辑

- 4.2.2 示例 2 – GPIO 输入滤波器

- 4.2.3 示例 4 – PWM 保护

- 4.2.4 示例 5 – 事件窗口

- 4.2.5 示例 6 – 信号生成和检查

- 4.2.6 示例 8 – 外部与门

- 4.2.7 示例 9 – 计时器

- 4.2.8 示例 10 – 具有两种状态的计时器

- 4.2.9 示例 11 – 中断标签

- 4.2.10 示例 12 – 输出相交

- 4.2.11 示例 17 - 单次 PWM 生成

- 4.2.12 示例 21 - 时钟预分频器和 NMI

- 4.2.13 示例 22 - 串行器

- 4.2.14 示例 23 - LFSR

- 4.2.15 示例 24 - 锁定输出屏蔽

- 4.2.16 示例 25 - 输入流水线模式

- 4.2.17 示例 26 - 计时流水线模式

- 4.3 专家示例

- 5在现有 DriverLib 工程中启用 CLB 工具

- 6常见问题解答 (FAQ)

- 7修订历史记录

1.2 CLB 配置过程概述

CLB 工具基于 CCS 中的 SysConfig 工具。生成的 C 头文件和源文件与 C2000Ware SDK 相结合,可以配置 CLB。要对设计进行仿真,需要安装许多第三方工具,包括编译器和波形查看器。有关 CLB 仿真器的更多信息,请参阅节 3.5。

CLB 工具生成一个“.dot”文件,该文件以方框图的形式显示子模块互连,有助于验证设计。此文件是使用 CCS 编译后处理步骤以 HTML 和 SVG 格式创建的。这些步骤使用了提供的示例中的 node.js 和 JavaScript 库。该工具还生成“clb_sim.cpp”文件。使用 GCC 编译器来编译 CPP 文件以及其他 CLB 仿真模型。编译的输出是一个“.exe”文件,必须在本地计算机上执行该文件以生成“.vcd”文件。该“.vcd”文件可用于通过外部图形查看器进行时序分析。所有这些步骤都通过该工具生成的“clb_simulation”文件完成。此文件为批处理 (.bat) 或 shell (.sh) 文件,具体取决于所使用的操作系统(本用户指南中使用的图像基于 Windows 操作系统)。必须执行此文件以生成适当的“.vcd”文件。

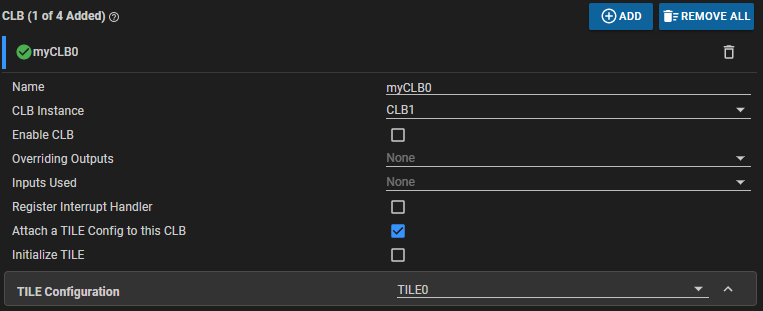

在生成的 C 头文件“clb_config.h”中对 CLB 配置进行编码。CLB 工具生成的“clb_config.c”文件使用生成的头文件将配置加载到 CLB 模块的寄存器中。SysConfig 中的 CLB 模块必须连接适当的 Tile Design 才能实际进行配置,如图 1-1 中所示。因为 SysConfig 中 Tile Design 与 CLB 模块互不相关,因此可以创建任意数量的逻辑块配置,而器件上的 CLB 实例数量有限。这些 Tile Design 有选择地加载到 CLB 中。

图 1-1 将 Tile Design 连接到 CLB 实例

图 1-1 将 Tile Design 连接到 CLB 实例请务必注意,在 C28x 器件的应用代码中,必须在执行器件初始化步骤期间调用“clb_config.c”文件中的函数。图 1-2 显示了 CLB 工具的输出以及 post-build 步骤。

图 1-2 CLB 工具工程结构

图 1-2 CLB 工具工程结构在典型情况下,用户从指定 CLB 逻辑功能开始。这可以采用逻辑电路图、时序信息、书面说明、VHDL 代码或其他形式。安装必需的工具后,第一步是连接逻辑块子模块以实现所需的逻辑。

指定内容可能包含一组时序图,在这种情况下,用户可以选择执行 CLB 配置的仿真,以确保行为符合预期。此步骤包括定义一组输入测试激励,以及构建一个仿真工程以生成可在图形查看器中打开的仿真波形。如果结果不符合预期,用户可以修改 CLB 工具设置并重复仿真。

在仿真产生正确的波形后,用户可以使用 CCS 将设计下载到器件中以运行或调试代码。

在为 C28x 器件启用了 SysConfig 的 CCS 工程中,创建 Tile Design 的 HTML 和 SVG 方框图的步骤是在编译后处理步骤中完成的。在用户构建 CCS 工程时,使用 C28x 编译器编译用户应用代码以及生成的“clb_config.h”和“clb_config.c”,并生成一个“.out”文件。

“clb_simulation”文件使用 GCC 编译器编译生成的仿真文件“clb_sim.cpp”和“clb_config.h”以及 CLB 仿真模式。此步骤的输出是“.exe”文件 (“simulation_output.exe”),该文件会自动运行以生成“CLB.vcd”文件。可以使用外部图形查看器来查看该文件。

图 1-3 CLB 工具构建过程

图 1-3 CLB 工具构建过程在 CLB 工具构建过程中,BUILD_CONFIG_LOC 目录是用作工程的构建配置输出的目录(这可以是“Debug”、“CPU1_RAM”等),并共用活动构建配置的名称。