ZHCU712B april 2020 – july 2023

- 1

- CLB 工具

- 商标

- 1引言

- 2开始使用

- 3使用 CLB 工具

-

4示例

- 4.1 基础示例

- 4.2

入门示例

- 4.2.1 示例 1 – 组合逻辑

- 4.2.2 示例 2 – GPIO 输入滤波器

- 4.2.3 示例 4 – PWM 保护

- 4.2.4 示例 5 – 事件窗口

- 4.2.5 示例 6 – 信号生成和检查

- 4.2.6 示例 8 – 外部与门

- 4.2.7 示例 9 – 计时器

- 4.2.8 示例 10 – 具有两种状态的计时器

- 4.2.9 示例 11 – 中断标签

- 4.2.10 示例 12 – 输出相交

- 4.2.11 示例 17 - 单次 PWM 生成

- 4.2.12 示例 21 - 时钟预分频器和 NMI

- 4.2.13 示例 22 - 串行器

- 4.2.14 示例 23 - LFSR

- 4.2.15 示例 24 - 锁定输出屏蔽

- 4.2.16 示例 25 - 输入流水线模式

- 4.2.17 示例 26 - 计时流水线模式

- 4.3 专家示例

- 5在现有 DriverLib 工程中启用 CLB 工具

- 6常见问题解答 (FAQ)

- 7修订历史记录

3.2 更新变量路径

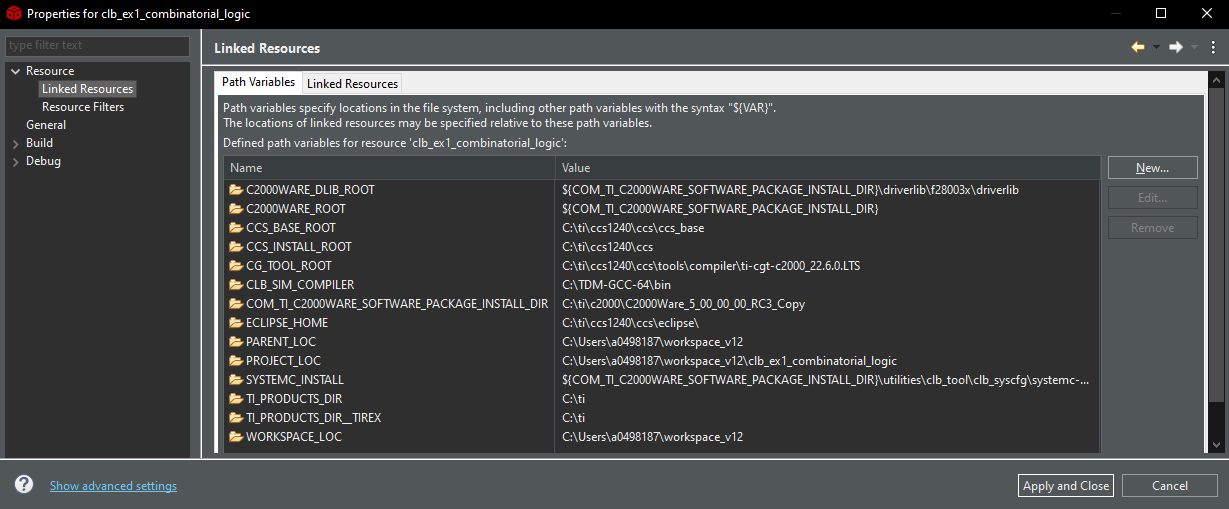

上面导入的空 CLB 工程不仅能够为 C28x 目标器件生成“.out”文件,而且能够生成设计的仿真文件和 HTML/SVG 方框图。要使用编译后处理步骤创建方框图,必须为 C2000Ware 根和节点工具的位置设置正确的路径。要仔细检查这些路径是否正确,请执行以下操作:

- 右键点击工程并选择“Project Properties”。

- 在“Resources”下,选择“Linked Resources”。

- 检查以确保下面的所有路径均正确:

- C2000WARE_ROOT(此路径用于 CLB 方框图和其他包含路径)

图 3-2 链接资源

图 3-2 链接资源

- C2000WARE_ROOT(此路径用于 CLB 方框图和其他包含路径)

- 如果名称左侧的图标不是文件夹,而是一个感叹号,则表示您的系统上不存在该路径,您必须手动选择正确的路径

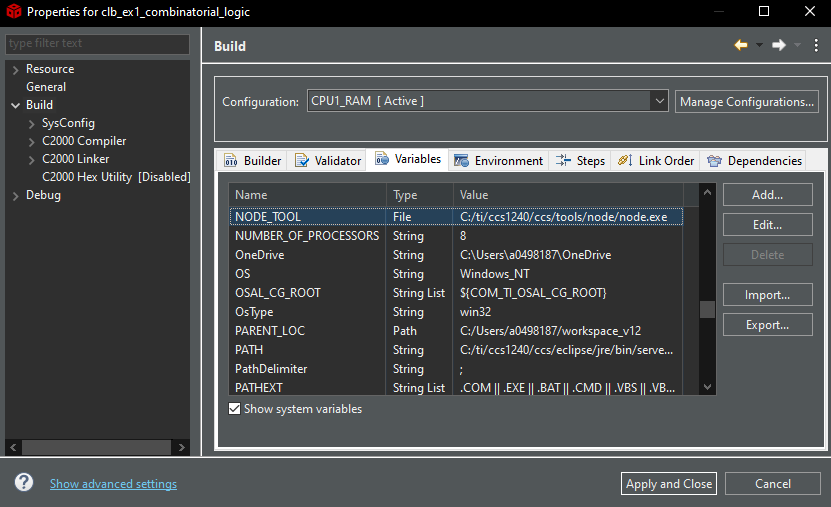

- 检查以确保以下系统变量的路径正确:

- NODE_TOOL

图 3-3 构建变量

图 3-3 构建变量

- NODE_TOOL

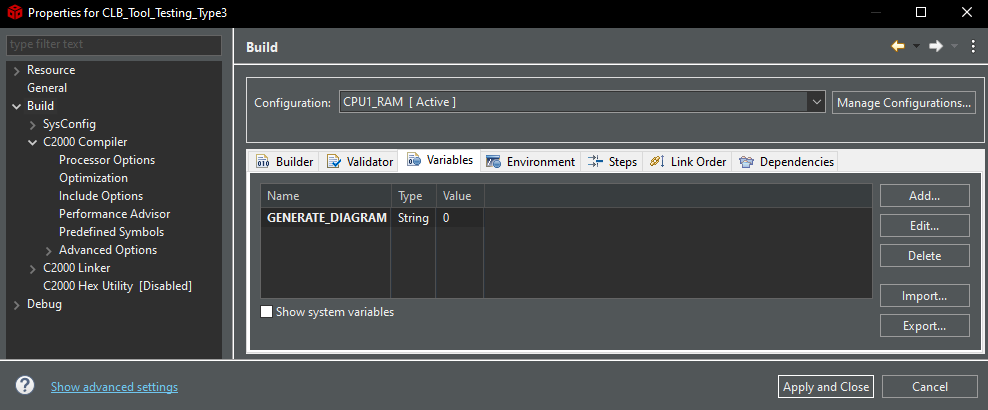

要生成方框图,必须将构建变量 GENERATE_DIAGRAM 设置为 1。通过转到“Project Properties”>“Build”>“Variables”,可以找到工程的构建变量,如图 3-4 中所示。此变量允许在构建工程后运行“Steps”下面列出的编译后处理步骤。这些方框图可以在工程相关构建配置下的“diagrams”目录中找到,如图 5-5 中所示。

注: 对于 Mac 和 Linux,编译后处理步骤中使用的条件将无法正确执行。要生成方框图,必须删除测试

if ${GENERATE_DIAGRAM} == 1。 图 3-4 用于生成方框图的构建变量

图 3-4 用于生成方框图的构建变量