ZHCAEN0A October 2024 – November 2025 MSPM0C1103 , MSPM0C1103-Q1 , MSPM0C1104 , MSPM0C1104-Q1 , MSPM0C1105 , MSPM0C1106 , MSPM0C1106-Q1 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G1518 , MSPM0G1519 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0G3518 , MSPM0G3518-Q1 , MSPM0G3519 , MSPM0G3519-Q1 , MSPM0H3216 , MSPM0H3216-Q1 , MSPM0L1105

4.1 MSPM0 的 ADC 配置

- 时钟

图 4-1 ADC 时钟的 Sysconfig 配置

图 4-1 ADC 时钟的 Sysconfig 配置- ADC 时钟(ADCCLK)

- SYSOSC(最大 32MHz)

- HFCLK(最大 48MHz)

- ULPCLK(最大 40MHz、仅支持 PD0)

- ADC 采样时钟 (SAMPCLK):由 ADCCLK 分频产生

- 转换时钟:ADC IP 内部的 80MHz 晶体振荡器

- 12 位 ADC 数据的转换时间大约为 14 个转换时钟周期

- ADC 时钟(ADCCLK)

- 采样模式

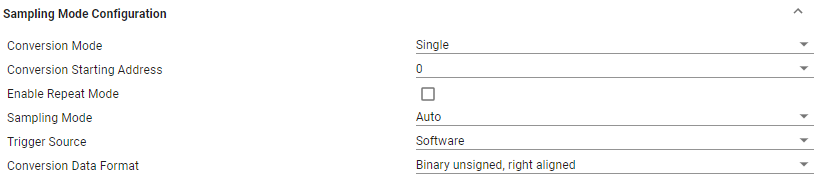

图 4-2 ADC 采样模式的 SysConfig 配置

图 4-2 ADC 采样模式的 SysConfig 配置 - 转换模式

- 单次转换:每次采样和转换过程仅转换单个点,通过配置起始地址 STARTADD,确定 MEMCTL 编号;

- 序列转换:通过定义用于转换的 MEMCTL 编号的起始地址 STARTADD 和结束地址 ENDADD,可以定义数据转换序列(MEMCTL0-11 对应 MEMRES0-11),并且可以为每个 MEMCTLx 配备不同的 ADC 通道;

- 启用重复模式

- 非重复模式:每一轮转换完成后,转换使能位 (ENC) 自动复位为零。

- 重复模式:转换过程将继续启用,直到软件清除转换使能位 (ENC);

- 采样触发源

- 软件:软件设置 CTL1.SC 位触发采样;

- 事件:事件上升沿触发采样;

- 采样模式

- 自动采样:采样触发信号生成后,采样信号 SAMPLE 自动上升,采样时间由 SCOMP 定义的若干 SAMPCLK 时钟周期确定;

- 手动采样(仅支持软件触发,不支持重复模式和序列转换,不支持硬件过采样):采样信号 SAMPLE 与软件触发信号 CTL1.SC 同步拉高。采样时间由 SC 的拉高时间确定,触发和采样同步完成;

- 触发模式

- 在重复和序列转换模式中,需要选择触发模式 (TRIG),以确定下一轮转换是否需要触发信号。

- 转换存储器配置

图 4-3 ADC 转换存储器的 SysConfig 配置

图 4-3 ADC 转换存储器的 SysConfig 配置 - 需要配置的转换存储器数量由转换模式中定义的 MEMCTL 起始和结束编号决定:

- 采样输入通道

- 基准电压

- VDDA:内部电源 (3.3V)

- VREF

- 内部:2.5V/1.4V

- 外部:0~3.3V

采样计时器源:在自动采样模式下,选择用于采样计时的计时器。

- 其他

- 过采样

- 采样结果倍数 = 采样点数/平均分母

- 中断

- 不使用 DMA:启用 MEMx 结果加载中断,每次采样结果生成后在中断中读取数据;

- 使用 DMA:启用 DMA 完成中断,根据 ADC MEMx 结果加载触发 DMA 数据传输,并设置 DMA 传输的数据量。一旦 DMA 传输完成,输入 DMA 中断,即可立即处理 ADC 采样数据。

CPU 轮询

- CPU 轮询 MEMx 结果加载寄存器,当 ADC 转换完成且结果载入 MEMx 时,相应的 CPU_INT RIS 位将置为 1。

- CPU 轮询 ADC 状态寄存器,当 ADC 转换完成时,ADC 状态忙位将被清零。注:

对于下列器件,在 CTL1 寄存器中 ADC 启动转换位置位后,经过 14 个 ULPCLK 周期,忙位将被置位。这 14 个 ULPCLK 周期需要 CPU 延迟来等待忙位置位,之后 CPU 可轮询忙位以等待其清零。建议使用 MEMx 结果加载寄存器来轮询 ADC 转换完成状态。

MSPM0C110x、L1x0x、L111x、L134x、Lx22x、Gx10x、Gx50x、Gx51x 和 H321x。

- 过采样