ZHCSRC3B December 2022 – March 2025 IWRL6432

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 功能方框图

- 5 器件比较

- 6 终端配置和功能

-

7 规格

- 7.1 绝对最大额定值

- 7.2 ESD 等级

- 7.3 上电小时数 (POH)

- 7.4 建议运行条件

- 7.5 一次性可编程 (OTP) 电子保险丝的 VPP 规格

- 7.6 电源规格

- 7.7 节电模式

- 7.8 每个电压轨的峰值电流要求

- 7.9 射频规格

- 7.10 支持的 DFE 特性

- 7.11 CPU 规格

- 7.12 热阻特性

- 7.13 时序和开关特性

- 8 详细说明

- 9 监控和诊断

- 10应用、实施和布局

- 11器件和文档支持

- 12修订历史记录

- 13机械、封装和可订购信息

8.4.1 用于用户应用的 GPADC 通道(服务)

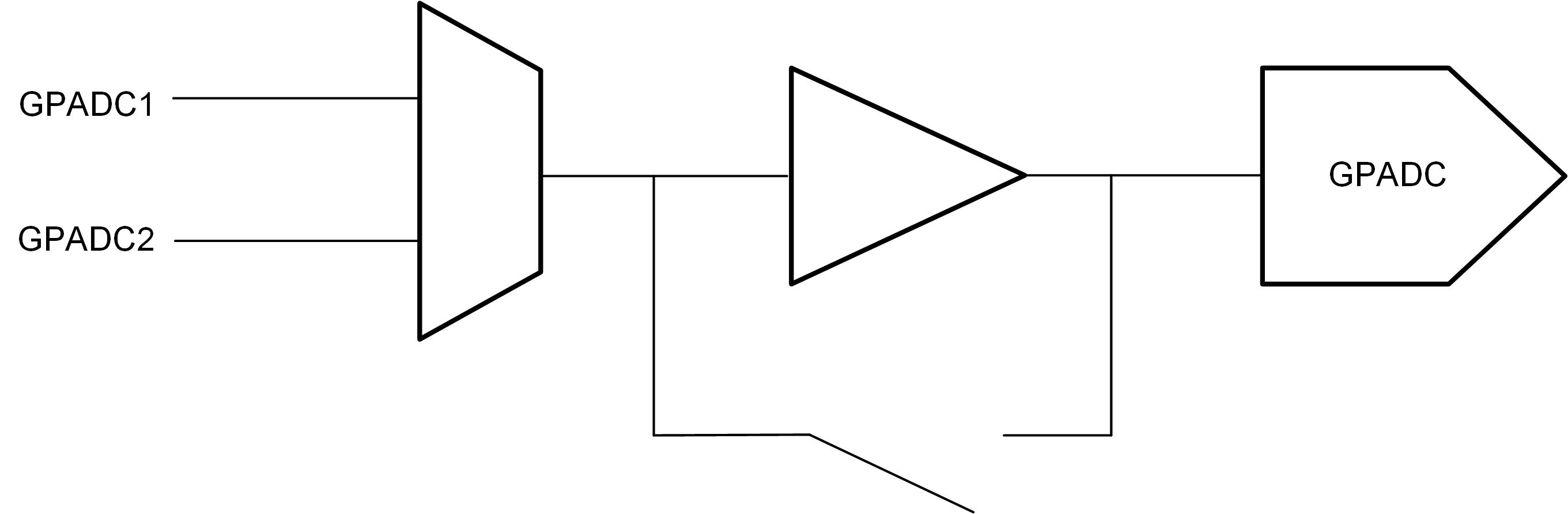

IWRL6432 器件包括为用户应用提供 ADC 服务,其中器件内部存在的 GPADC 引擎可用于测量多达两个外部电压。GPADC1 和 GPADC2 引脚用于此目的。

- GPADC 本身由在 FEC 子系统内部运行的 TI 固件进行控制,通过路由到 FEC 子系统的“APPSS”调用对其进行访问以实现客户的外部电压监控目的。此 API 可以与在 APPSS Cortex M4F® 上运行的用户应用程序链接。

- 器件固件包 (DFP) 提供 API 来配置和测量这些信号。这些 API 允许配置稳定时间(要跳过的 ADC 样本数)和要采集的连续样本数。在帧结束时,将报告每个受监测电压读数的最小值、最大值和平均值。

图 8-7 GPADC 路径

图 8-7 GPADC 路径GPADC 结构用于测量内部温度传感器的输出。这些测量的精度为 ±7°C。