ZHCUA86A May 2021 – May 2022 DAC12DL3200

- 摘要

- 商标

- 1引言

- 2设备

-

3设置过程

- 3.1 安装 High-Speed Data Converter (HSDC) Pro 软件

- 3.2 安装配置 GUI 软件

- 3.3 连接 DAC12DL3200EVM 和 TSW14DL3200EVM

- 3.4 将电源连接到电路板(关闭)

- 3.5 将信号发生器连接到 EVM(*在定向之前禁用射频输出)

- 3.6 打开 TSW14DL3200EVM 的 12V 电源并连接到 PC

- 3.7 打开 DAC12DL3200EVM 的 5V 电源并连接到 PC

- 3.8 打开信号发生器射频输出

- 3.9 打开 DAC12DL3200EVM GUI 并对 DAC 以及适用于单通道 NRZ 模式 2 运行的时钟进行编程

- 3.10 打开 HSDC 软件并将 FPGA 图像加载至 TSW14DL3200EVM

- 3.11 DxSTRB 定时调整

- 4其他工作模式

- 5寄存器日志文件

- 6器件配置

- A DAC12DL3200EVM 疑难解答

- B DAC12DL3200EVM 板载时钟配置

1 引言

DAC12DL3200 是一款延迟超低的双通道 12 位射频采样数模转换器 (DAC),采样速率在双通道模式下高达 3.2 千兆样本/秒 (GSPS),或在单通道模式下高达 6.4GSPS。当使用多种奈奎斯特输出模式时,DAC 可以在接近 8GHz 的载波频率下传输超过 2GHz 的信号带宽。DAC12DL3200EVM 器件的输入数据通过高速 LVDS 接口进行传输。此评估板还包括以下重要特性:

- 变压器耦合输出支持高达 8GHz 的单端 50Ω 输出信号

- LMX2592 时钟合成器,作为生成 DAC 采样时钟的选项

- 针对支持外部时钟源的快速设置的变压器耦合输入时钟选项(电路板默认设置)

- 适用于 DAC SYSREF 和 FPGA 参考时钟源的 LMK04828 时钟合成器

- 通过 USB 连接器和 FTDI USB 转 SPI 总线转换器进行器件寄存器编程

- 通过 400 引脚 FMC 接口连接器实现高速 LVDS 数据输入

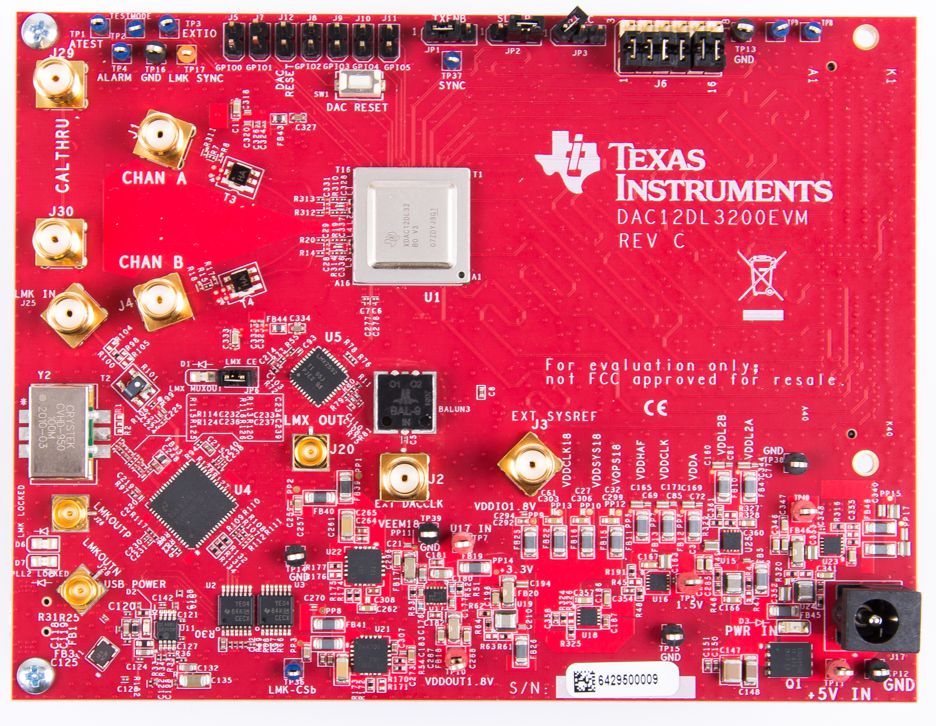

图 1-1 DAC12DL3200EVM

图 1-1 DAC12DL3200EVMTI TSW14DL3200EVM 图形发生器与 TI High-Speed-Data-Converter (HSDC) Pro 软件 GUI 搭配使用,可将 LVDS 数据测试图形发送到 DAC12DL3200EVM。

在 HSDC Pro 软件中正确选择硬件后,将自动配置 TSW14DL3200EVM 以支持 DAC12DL3200 的不同运行模式。接口提供高达 1600MSPS 的 LVDS 输出数据。