ZHCACV2 july 2023

3.1.2 软件架构

工程流程包含使用 AM263x SysConfig 工具和 MCU_PLUS_SDK_AM263x 对片上系统 (SOC) 的所有外设时钟和子模块进行初始化的过程。节 3.2讨论了如何初始化该设计中使用的外设 IP,如 EPWM、ADC、CMPSS、GPIO、SDFM 等。

此软件包含 2 个 ISR 和 1 个后台任务。图 3-2 中介绍了代码流程。ISR1 计划每 20μs 运行一次,ISR2 计划每 1ms 运行一次。ISR1包含节 3.3.1中所述的主控制环路。ISR2 包含辅助控制功能,如计算用于后台监视的相电流和电压的 RMS 值,节 3.3.3对此进行了说明。

图 3-2 软件方框图

图 3-2 软件方框图该工程有两个版本的 ADC 检测数据,具体取决于 controlCARD 的版本(E1 和 E2)。如果正在使用的电路板是 controlCARD 的 E1 版本,则启用宏 AM263x_CC_E1。或者,如果正在使用的电路板是 controlCARD 的 E2 版本,则启用宏 AM263x_CC_E2。这些宏设置在 Source/Includes 文件夹中的 tinv_user_settings.h 文件中定义。根据使用的电路板版本选择 .syscfg 文件,并从构建中排除另一个文件:对于 E1 controlCARD,此文件为 tinv_AM263x_E1.syscfg;对于 E2 controlCARD,此文件为 tinv_AM263x_E2.syscfg。

后台任务分为四个部分 – A1、B1、B2 和 B3。每次所连接的计时器溢出时,即延迟为由 RTI 计时器控制的 1ms,都会执行 A1。之前在 C2000 架构中使用 A1 来运行 SFRA 环路,目前 A1 保持开路,因为不支持 SFRA。

B1、B2 和 B3 通过带有 RTI 计时器的 1ms 延迟控制器依次执行。节 3.2.3对此配置进行了说明。B2 任务通过捕获 ISR 上的 GPIO 高波形和低波形,使用 ECAP 计算 ISR1 和 ISR2 的 CPU 负载时间和平均 CPU 负载时间。B3 任务监视连接到 TIDA-01606 的风扇和继电器控制。B1 任务更新系统的故障状态。通过将宏 TINV_PROTECTION 设置为 TINV_PROTECTION_ENABLED,可启用此设置。默认情况下,实验 1 禁用此步骤,而其他实验则启用此步骤。有关这方面的更多信息,请参阅节 3.4。

以下库取自 C2000 Digital Power SDK 工具套件,并集成了逆变器演示工程。

- Transforms 库:此库用于执行 Clarke 和 Park 变换函数。三相交流波形具有三种不同的量,因此很难控制输出波形并在全部三个波形之间实现同步。因此,必须将波形转换为直流域,以应用与控制增益相关的计算。

- ABC 至 DQ → Clarke + Park 变换。这会将三相量转换为旋转坐标系中的直流量,以实现正序列和负序列。

- DQ 至 ABC → 逆向 Park + 逆向 Clarke 变换。这会将旋转坐标系中的直流量转换为时域中的三相量。这两种变换完全通过软件计算实现。

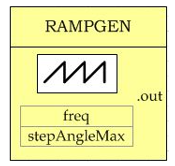

- Rampgen 库:此库提供一组可生成所需频率的斜坡信号的函数。在逆变器运行模式下,需要使用基准斜坡信号来计算 50Hz 正弦波输出所需的 PLL 角度。

图 3-3 Rampgen 模型

图 3-3 Rampgen 模型 - SPLL – 软件锁相环 (PLL):这款基于软件的 PLL 代码基于三相电网连接的同步坐标系。首先,检测并记录三个相电压 A、B 和 C。然后将这些电压转换为直流分量 D 和 Q。要确保三相系统是同步的;Q 值必须接近零。SPLL 使用该设定点生成下一个 θ,以提供有效输出。适用于三相并网应用并采用 C2000™ 微控制器的软件锁相环设计 应用手册中对这些信息进行了深入介绍。

图 3-4 控制 ISR 中的 SPLL 使用流程

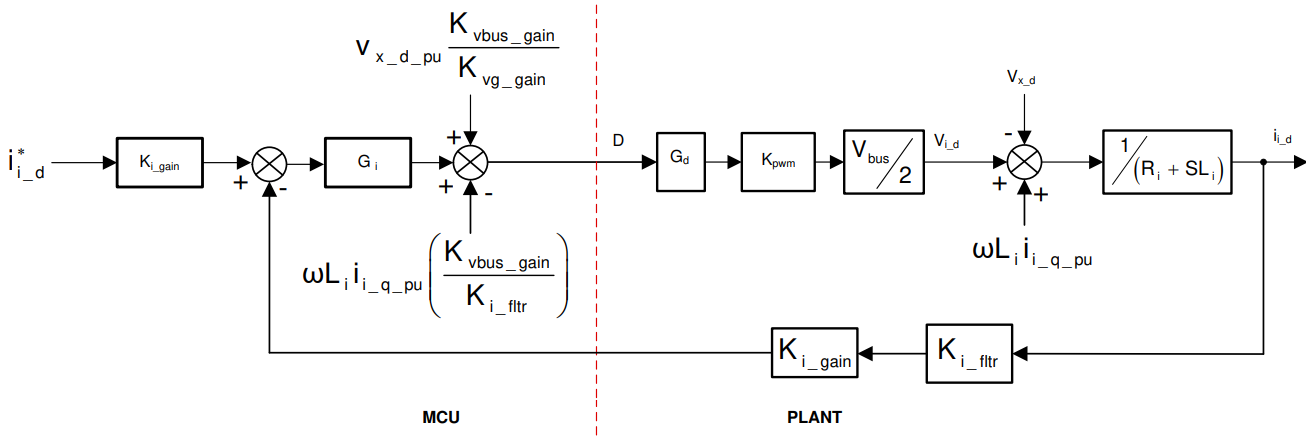

- PIC 控制器库:本演示使用比例积分控制环路 (PI) 来维持输出电流。用户为系统选择基准电流值。无论输入如何,PI 控制器都必须在系统中保持该电流。可根据 Ia、Ib 和 Ic 计算 Id 和 Iq 值。现在将生成的 Id 与基准 Id 进行比较,并计算出误差。接下来,确定 PWM 的脉冲宽度,从而调节输出电流。图 3-5 显示了电流控制环路的方框图。10kW 双向三相三级(T 型)逆变器和 PFC 参考设计 设计指南的控制设计部分介绍了 PIC 控制器的计算。

- i*i_d = 电流基准

- Ki_gain = 电流检测标量,是最大电流检测值的倒数

- Ki_fltr 是在电流检测路径上连接的滤波器。电流检测标量,是最大电流检测值的倒数

- Kvbus_gain = 总线的电压检测标量,是最大电压检测值的倒数

- Kvg_gain = 电网电压的电压检测标量,是最大电压检测值的倒数