ZHCACV2 july 2023

4 实施优化

在逆变器演示中,使用以下技术来优化 ISR 的执行时间:

- 构建设置更改为带有优化的释放模式。

- 将代码添加至 TCM 以加快执行速度。TCM 具有低延迟,通过 TCM 访问的指令占用一个 CPU 周期。

- 在 TCM 中执行 ISR 以加快代码创建速度。ISR 内执行的所有变量均为全局变量并添加到 TCM 中。

- 自定义节添加到 linker.cmd 文件的 TCM 部分中。变量是添加到单独 TCM 部分的函数,可避免冲突。

- .controlfnc : {} palign(8) > R5F_TCMA

- .controldata : {} palign(8) > R5F_TCMB

- 在函数原型中使用 __section__("SECTION_NAME") 属性,以将其添加到 TCM 中。

- always_inline 属性用于强制 API 进入内联函数。

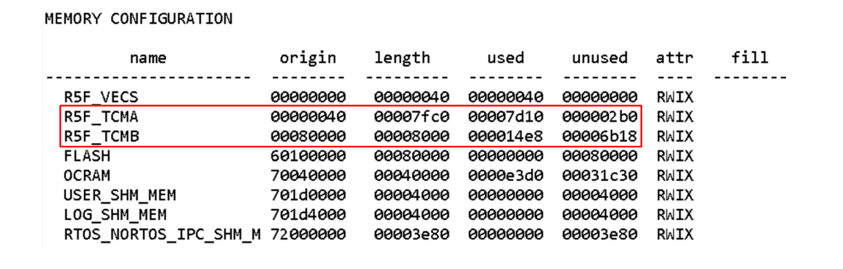

- 图 4-1 列出了实验 3 的 TCM 存储器消耗

图 4-1 启用实验 3 时的 TCMA 和 TCMB 存储器消耗

图 4-1 启用实验 3 时的 TCMA 和 TCMB 存储器消耗- 三角计算被 r5_math_Trig 库函数取代。

- MCU_PLUS_SDK 具有 r5_math_Trig 库,与标准 mathlib 相比,该库具有优化的三角运算。

- sinf(TINV_angleSPLL_radians) → ti_r5fmath_sin(TINV_angleSPLL_radians, ti_r5fmath_PIconst, ti_r5fmath_sinCoef)

- 一次 sinf 计算大约消耗 0.45μs 的执行时间。这可以用高级三角函数库 API 取而代之,后者进行一次正弦运算消耗 0.12μs。

- 如果相邻的 16 位 ADC 读操作转换为 32 位读操作且值被划分为 16 位,则进行两次 16 位 ADC 读操作。

- 妥善做法是在一组中配置 ADC 检测功能。例如,CSL_ADC_RESULT_ADCRESULT0 和 CSL_ADC_RESULT_ADCRESULT1 可以同时配置和读取。

- 寄存器上的读取操作成本高昂,该方法将读取操作减少了一次。

#define CSL_ADC_RESULT_ADCRESULT0 (0x00000000U) #define CSL_ADC_RESULT_ADCRESULT1 (0x00000002U) #define CSL_ADC_RESULT_ADCRESULT2 (0x00000004U) #define CSL_ADC_RESULT_ADCRESULT3 (0x00000006U)

- 修改 ADC 和 PWM 寄存器空间的 MPU 配置以启用已发布的写入。这会配置 MPU 区域访问控制寄存器位分配。

- 所有寄存器写入操作默认严格排序,也就是说,数据首先写入寄存器,并且 CPU 会等待 Ack 成功写入然后再进行下一次写入。

- 删除严格排序配置将启用连续写入操作。根据要求,可以将配置设置为可缓存或不可缓存。通常,为加快执行速度,优选不可缓存,因为不会占用 CPU 周期来缓存数据。

- 这可以与 DMA 相结合,以便及时发送多个寄存器数据(在本文档发布时,尚未实现此功能)。

- 有关更多信息,请参阅 Cortex-R4F 技术参考手册的 MPU 寄存器部分。

- 更多编译器优化:

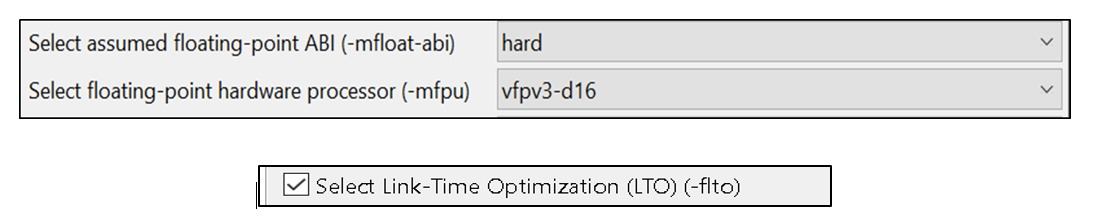

- Arm® Cortex® – R5 将涉及浮点的算术和逻辑计算卸载到 FPU,从而提高速度和运算能力。选择浮点 abi 作为硬配置,以使用 FPU 硬件进行运算,而不是进行软件计算。

图 4-2 编译器优化设置

图 4-2 编译器优化设置- 链接时优化:

- 将编译器优化配置为 TIARM Clang 2.1 LTS 中支持的 -flto(链接时优化 - LTO)。

- 要访问 -flto 功能,需要将编译器配置为 CCS 工程中受支持的版本。

- 依次转到“Project Properties”→“Arm Compiler”→“Optimizations”→“Select Link-Time Optimization Option (LTO)”,如图 4-2 中所示。

- 启用设置并重新构建工程后,请检查 ltoN 选项的映射文件,它表示正在使用 LTO 选项的位置。

- 映射文件还表明,.rodata 输出段在支持 LTO 的 -Oz 构建中要小得多。

- 有关更多详细信息,请参阅编译器工具用户手册 中的链接时优化 部分。