ZHCUD52 July 2025

3.3.3 1V5_GTY

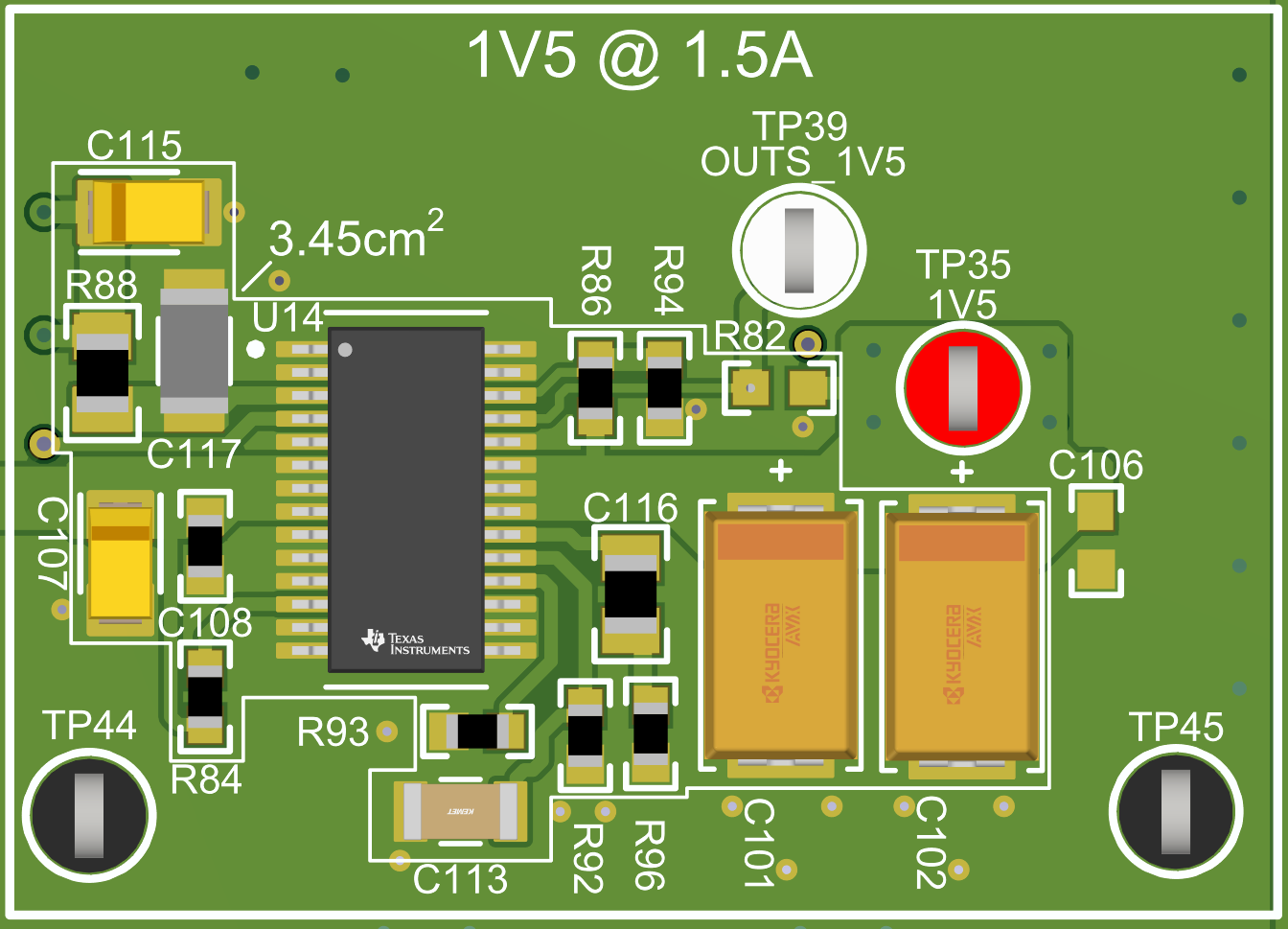

选择 TPS7H1111-SEP 从 2V5_DDR 电源轨生成 1.5V 电源轨(对于偏置,选择 3V3_VCCO)。虽然 TPS7H1111-SEP 能够提供 1.5A 电流,但 Versal Edge VGTY_AVCCAUX 电源轨估计只需要 0.05A 电流。因此,LDO 的最大设计电流为 0.2A,以提供合理的裕度。

本设计选择 EVM 上使用 2 个 100μF 输出电容器。无需添加额外的陶瓷去耦电容器,因为 TPS7H1111-SEP 不需要它们即可实现良好的性能。但是,如果需要,可以在 FPGA 负载附近添加一个 100nF 电容器(布局中为此目的预留了位置)。设置 FB_PG 电阻器的大小,以使 PG 置为有效阈值出现在 VOUT 的 94.9% 处。必须仔细选择该阈值,以确保在启动期间 TPS7H1111-SEP 的电压在 Versal FPGA 的最大时序要求范围内斜升。此外,选择一个 2.2μF CSS 电容器而不是典型的 4.7μF 电容器,以便在启动期间提供额外的时序裕度。4.7μF 电容器提供的低噪声经确定对 Versal FPGA 并非关键要求。

图 3-17 显示了 1V5_GTY 原理图,图 3-20 显示了布局。

图 3-19 1V5_GTY 原理图

图 3-19 1V5_GTY 原理图 图 3-20 1V5_GTY 布局

图 3-20 1V5_GTY 布局