ZHCUCJ2 November 2024 F29H850TU , F29H859TU-Q1

2.1.1 外设中断优先级和扩展 (PIPE)

在 C28x 中,主中断控制器是外设中断扩展 (PIE)。在 C29x 中,主中断控制器是外设中断优先级和扩展 (PIPE)。PIPE 模块对器件上的外设中断进行仲裁。每个时钟周期对所有产生的中断进行仲裁,优先级最高的中断施加到相应的 CPU 中断线路(NMI、RTINT 或 INT)。PIPE 模块负责为 CPU 提供 NMI、RTINT、INT 和 RESET 矢量地址。PIPE 能够定制中断和硬件嵌套的顺序。有关更多信息,请参阅 F29H85x 和 F29P58x 实时微控制器技术参考手册。

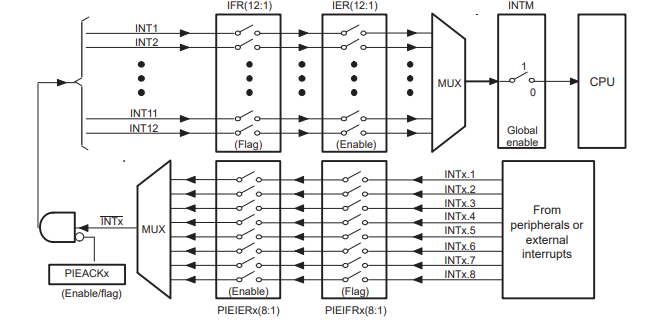

图 2-1 PIE 架构

图 2-1 PIE 架构 图 2-2 PIPE 架构

图 2-2 PIPE 架构表 2-2 PIE 与 PIPE

| 特性 | C28x PIE | C29x PIPE |

|---|---|---|

| 硬件优先级划分 | 否(仅软件) | 是 |

| 硬件仲裁 | 否(仅软件) | 是 |

| 硬件嵌套 | 否 | 是(可以使用组阻止) |

| 外设中断类型 | 1 | 2 (RTINT/INT) |

| 栈溢出跟踪 | 否 | 是 |

| 外设中断计数 | 192(在大多数器件上) | 256 |