ZHCUBL6 December 2023 CC3300 , CC3300MOD , CC3301 , CC3301MOD , CC3351 , CC3351MOD

3.3 射频 (RF)

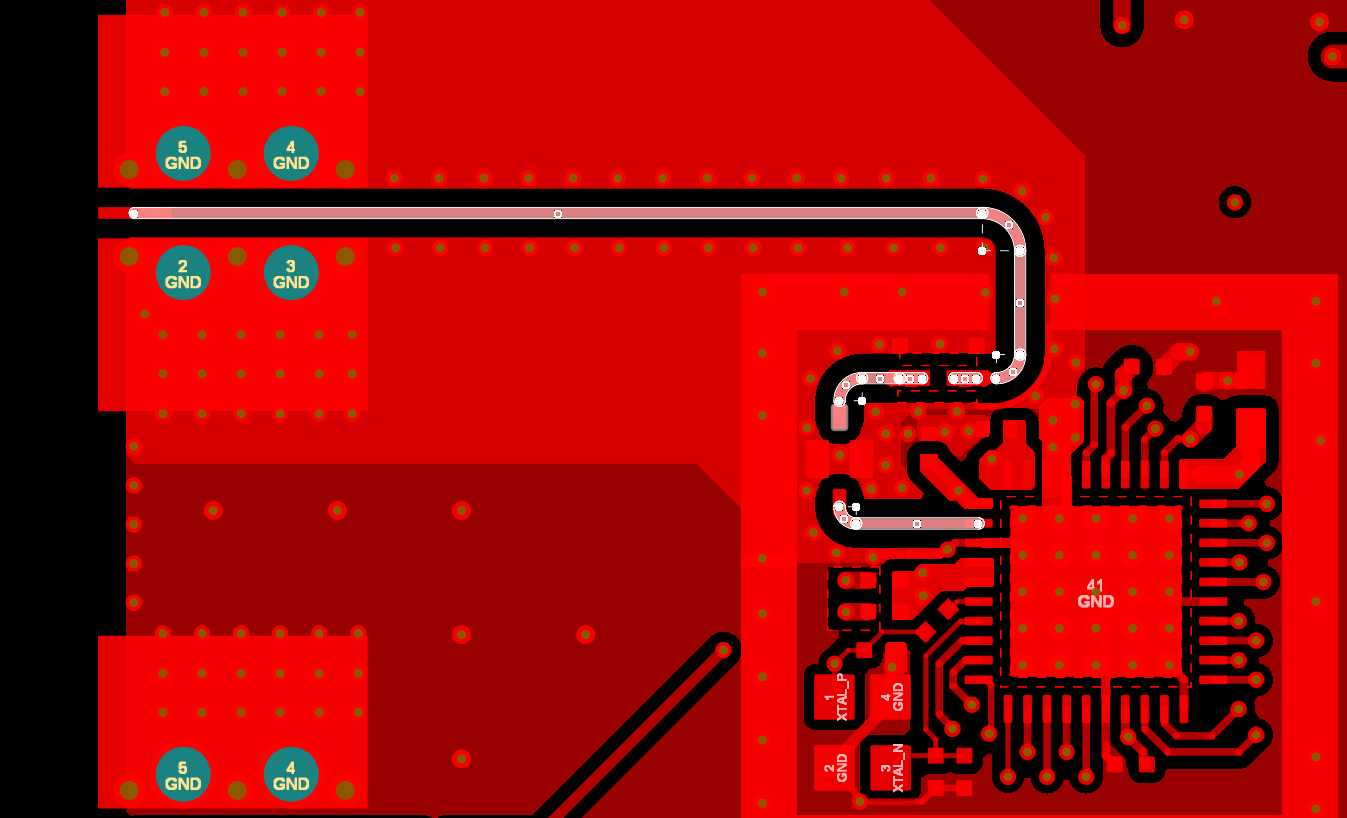

下面的图 3-8 显示了参考设计中的射频部分。为了达到峰值性能,设计布局的这个区域时必须特别小心。不良布局会导致输出功率、EVM、灵敏度和频谱屏蔽的性能下降。

图 3-8 是从 CC330x 参考设计文件中提取的样图。

图 3-8 参考设计射频路径

图 3-8 参考设计射频路径除了尽可能遵循参考设计,还请遵守下面所列的指导原则。

- 射频布线应具有恒定的 50Ω 特性阻抗。通过根据电介质、层堆叠、接地屏幕间距和布线厚度来匹配 CPWG,从而实现此阻抗。这些参数在整个布线长度上应保持一致。

- 整个射频布线只应位于 PCB 的顶层,并且紧挨着下面的层应是一个恒定的接地平面(XTAL 切口除外)作为布线参考。

- 射频布线应尽可能干净、笔直,在天线之前,除了带通滤波器和匹配滤波器之外没有任何元件。这是为了避免不必要的元件与元件耦合。如果不能使用直射频布线,则可接受圆形曲线。

- 射频布线应尽可能与其他元件隔离来减少噪声。接地平面应环绕射频布线,且接地过孔拼接之间的距离应小于最小波长的 1/8。

- 带通滤波器应尽可能远离 RF_BG 引脚(引脚 2)以及引脚 4 和 5 上的 VDDA 去耦电容器(在设计空间限制范围内)。

- 应在带通滤波器 (BPF) 的两个接地焊盘之间放置一个接地过孔。应连接 BPF 两侧的接地平面,以便为整个区域启用一个公共接地平面。在 BPF 和 PA_LDO_OUT 去耦电容器(引脚 1)之间的接地平面中,应增加接地过孔拼接。

- 射频布线附近不应有高频信号布线或测试点。

影响射频性能地另一个有效因素是堆叠。例如,表 3-1 包含 BP-CC3301 设计中使用的堆叠(从上到下)。

表 3-1 所有 CC33xx EVM 中使用的堆叠(从上到下)

| 层 | 名称 | 厚度 | εr |

|---|---|---|---|

| 顶部阻焊层 | |||

| 顶部焊接 | 1.00mil | 3.5 | |

| 1 | 顶层 | 1.85mil | |

| 电介质 1 | 5.48mil | 4.2 | |

| 2 | L02_GND | 1.26mil | |

| 电介质 2 | 42.82mil | 4.2 | |

| 3 | L03_PWR | 1.26mil | |

| 电介质 3 | 5.48mil | 4.2 | |

| 4 | 底层 | 1.85mil | |

| 底部阻焊层 | 1.00mil | 3.5 | |

| 底部阻焊层 |

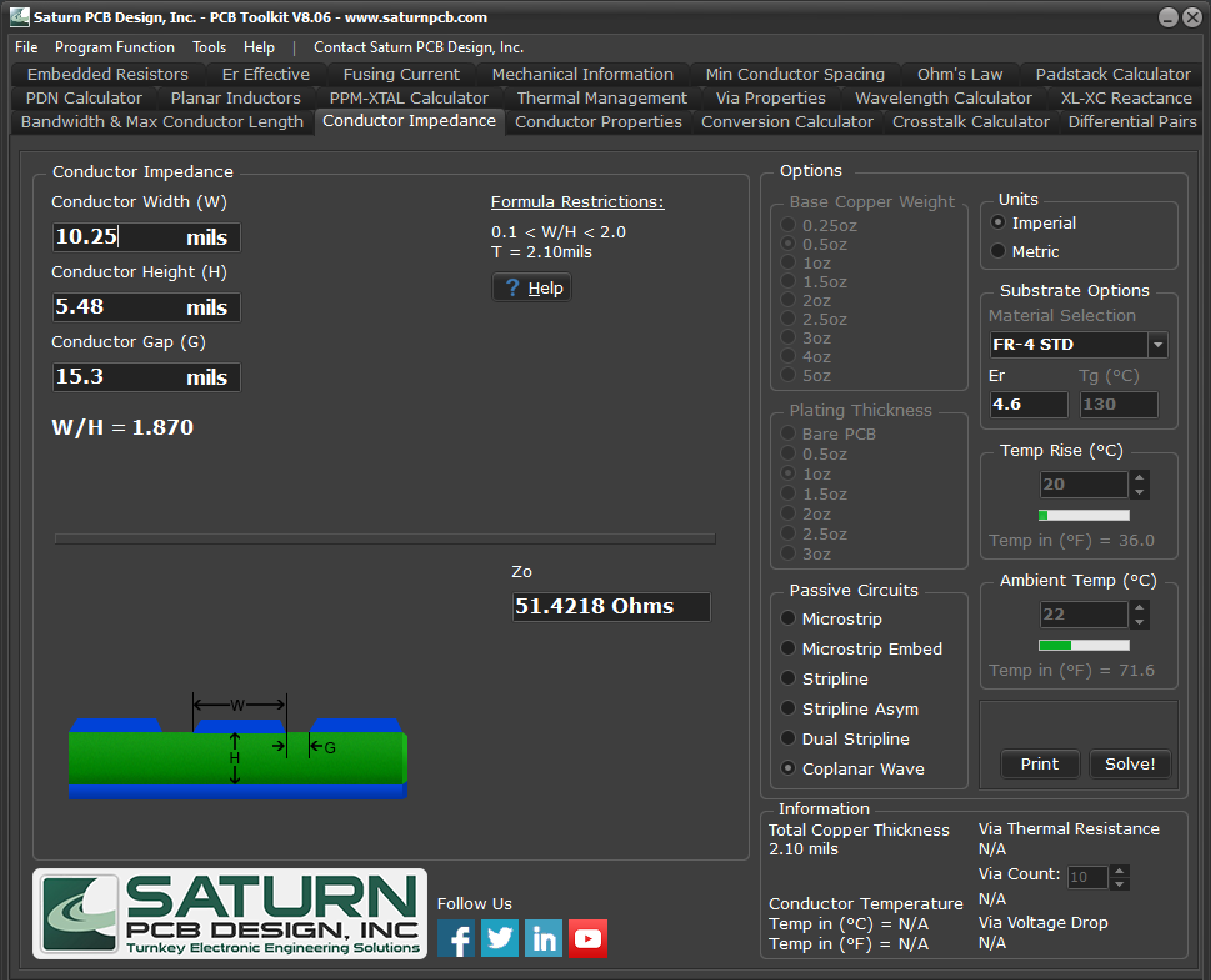

来自器件的射频信号使用共面波导 (CPW-G) 结构路由到天线。此结构为滤波器间隙实现更大程度的隔离,为射频线路提供更好的屏蔽。为了实现 50 欧姆的阻抗,必须考虑堆叠和布线测量。图 3-9 和图 3-10 以 BP-CC3301 EVM 为例展示了计算布线阻抗的示例。

此图像来自 BP-CC3301 设计文件。

图 3-9 进行射频布线测量的示例

图 3-9 进行射频布线测量的示例 图 3-10 计算布线阻抗的示例

图 3-10 计算布线阻抗的示例