ZHCABI7 March 2022 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.2 SR PWM 占空比限制

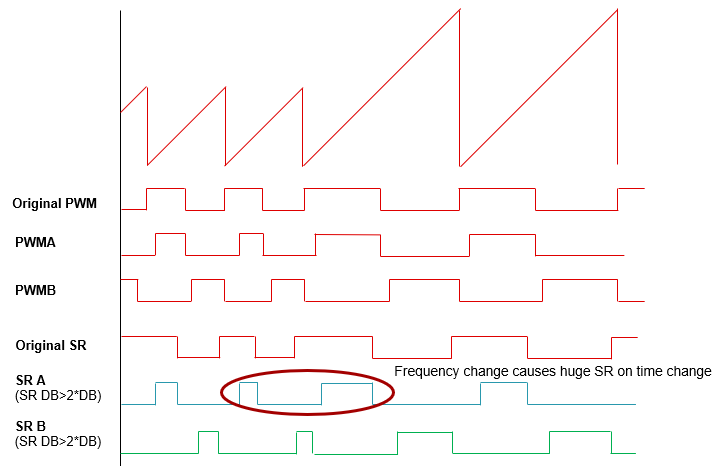

图 3-2 表示 SR 开通时间超过 LLC 转换器谐振周期的工作条件。如果 PWM 周期实际跨越 2 个 PWM 计数器周期,那么当频率发生巨大变化时,可能会造成 PWM 波形紊乱。

当 PWM 频率低于 LLC 谐振频率时,需要限制 SR 开关的开通时间。否则,SR MOS 上会存在反向电流,这会严重影响转换器的效率,甚至会因为体二极管的反向恢复而使转换器面临危险。

图 3-2 SR 开通时间变化示例

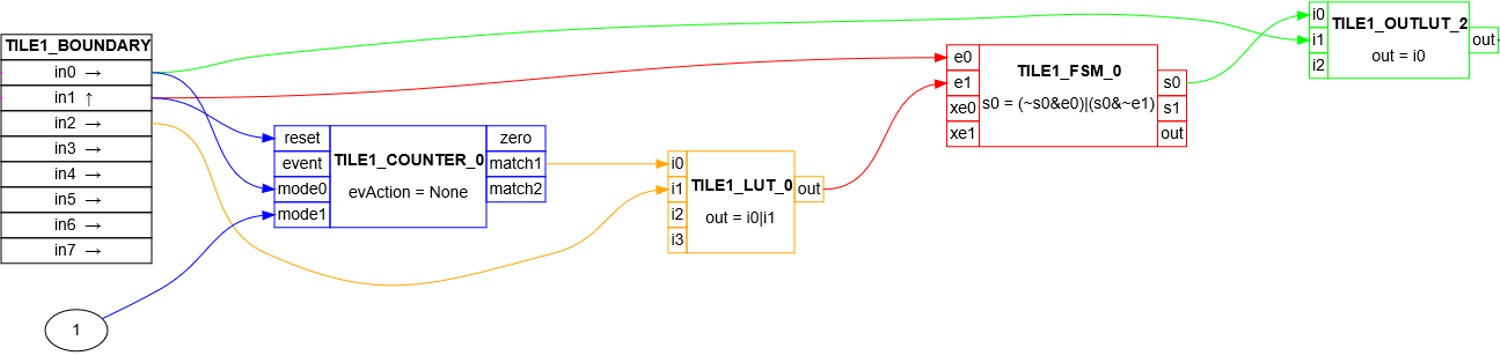

图 3-2 SR 开通时间变化示例第 3 代 C2000 器件的 CLB 模块使之很容易实现高度灵活的 PWM 波形。限制 PWM 开通时间的 CLB 设计如图 3-3 所示。

图 3-3 CLB 配置

图 3-3 CLB 配置在此设计中,配置了计数器,以限制 SR PWM 的最大开通时间。计数器在收到 SR PWM 上升沿后开始计数,并在达到配置的匹配值时生成一个脉冲(匹配 1)。匹配值通过 CLB 时钟计数决定最大开通时间。

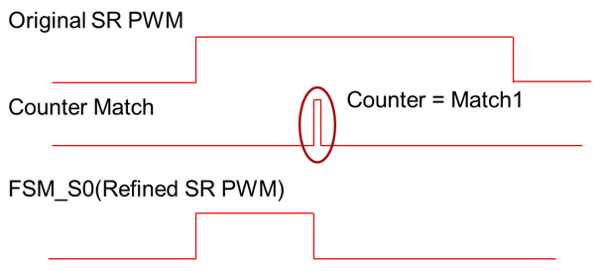

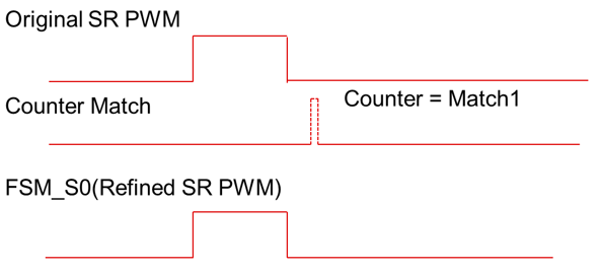

在 LUT0 中,输入为 2 时匹配信号是“ORed”,这是原始 SR PWM 的下降沿,然后 PWM 连接到 FSM_0。通过正确配置 FSM,e0(原始 PWM 上升沿)能够拉高 FSM_S0 的 S0,e1(原始 PWM 的下降沿或计数器 0 匹配信号)能够拉低 S0。通过这样做,S0 成为优化的 PWM,如果开通时间超过最大值,可以拉低它。图 3-4 显示了 CLB 内部信号的波形。

图 3-4 CLB 内部波形

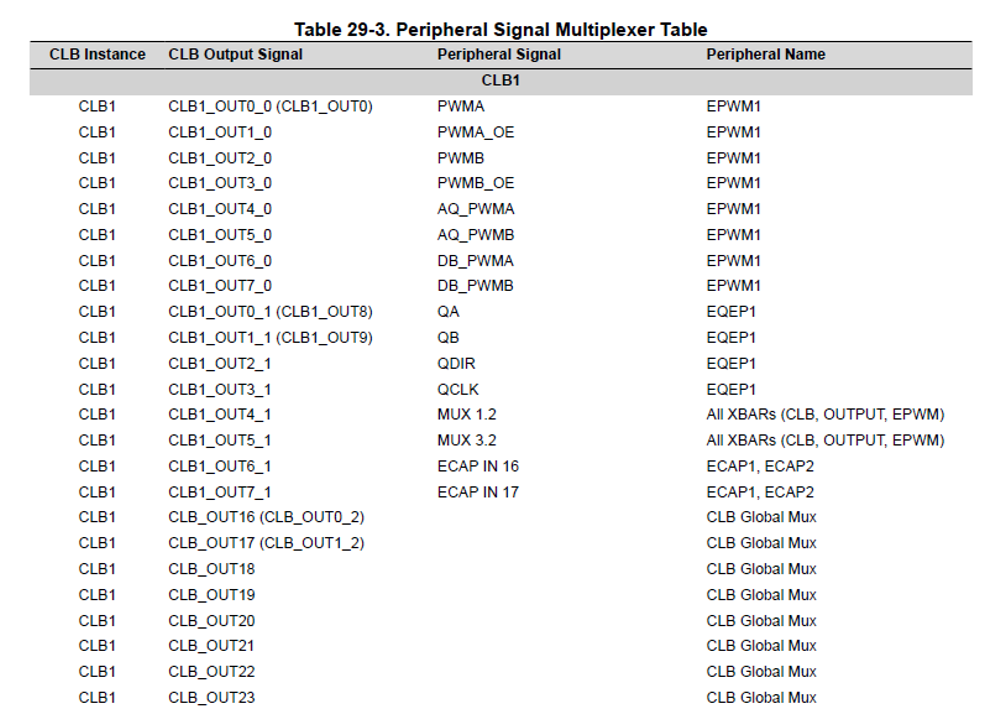

图 3-4 CLB 内部波形最终,FSM_S0 可通过 OUTLUT 成为 CLB 输出,并通过配置 CLB 输出多路复用器最后作为 PWM 输出折回。

图 3-5 多 CLB 输出通过多路器连接到外设

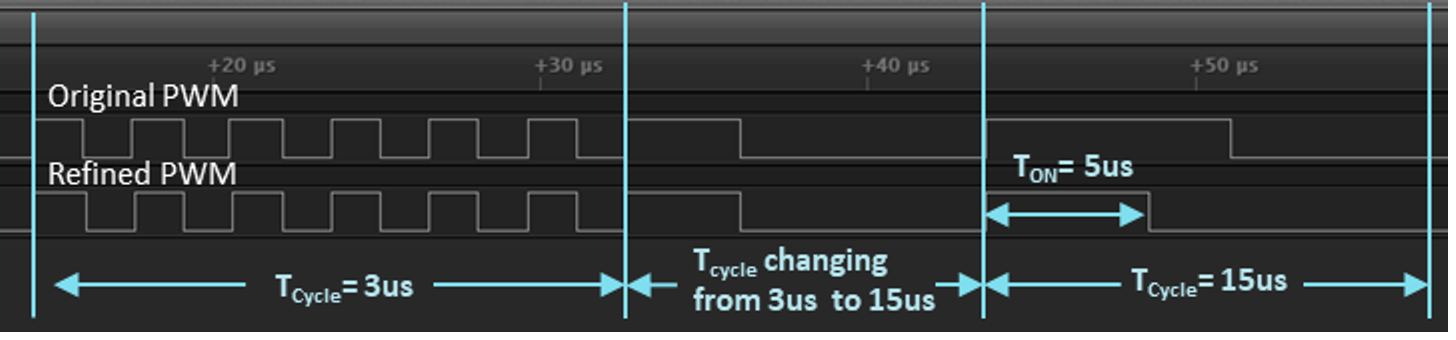

图 3-5 多 CLB 输出通过多路器连接到外设图 3-6 显示 PWM 周期从 3µs 变为 15µs、同时最大开通时间限制为 5µs 时的波形。如波形所示,当开通时间达到 5μs 时,优化的 PWM 立即拉下,因此该特性可以用来限制 LLC 转换器中 SR FET 的反向电流。

图 3-6 PWM 限制

图 3-6 PWM 限制