ZHCABI7 March 2022 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.2 次级侧

随着对 LLC 拓扑效率的要求不断提高,同步整流已变得必不可少。由于初级侧和次级侧之间以及相位之间的时序复杂,所以 MCU 历来很难处理多相同步整流拓扑。然而,灵活的 4 类 PWM 使之在 C2000 上成为可能。

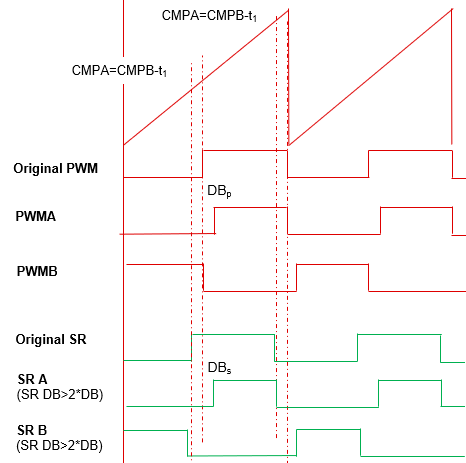

图 2-5 显示同步整流 (SR) MOS 的 PWM 配置。请注意,SR 从初级侧使用单独的 PWM 模块,因此一组新的 CMPA 和 CMPB 可以搭配新的动作限定器事件使用。为确保 SR FET 安全运行,SR FET 设置为比初级侧 FET 略早关断,方法是设置 CMPAS = CMPAP-t1 和 CMPBS= CMPBP- t1。同时,对应的 SR 也要比初级侧开关晚开通,因此采用 AHC 模式延迟原始 SR 信号的上升沿,生成 SRA 和互补 SRB 的 PWM。考虑到初级侧 PWM 存在死区,次级侧死区必须足够大,才能确保 SRx 不会早于初级侧开通:

DBs>t1+DBp

为了便于计算,我们可以设置 t1= DBp,因此:

DBs>2*DBp

图 2-5 SR MOS PWM 配置

图 2-5 SR MOS PWM 配置