SPRAD28 October 2022 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2-Q1 , AM263P4 , AM263P4-Q1 , AM26C31-EP , AM26C31M , AM26C32-EP , AM26C32C , AM26C32M , AM26LS31M , AM26LS32AM , AM26LS33A-SP , AM26LS33AM , AM26LV31E-EP , AM26LV32E-EP , AM26S10 , AM2732 , AM2732-Q1

- Abstract

- Trademarks

- 1 Building for Debug

- 2 Code Composer Studio Stop-Mode Debugging

- 3 Debug Logging

- 4 Multi-Core Debug

- 5 Debugging Arm Cortex-R5 Exceptions

- 6 Debugging Arm Cortex-M4 Exceptions

- 7 Debugging Memory

- 8 Debugging Boot

- 9 Debugging Real-Time Control Loops

- 10E2E Support Forums

5.2.1.2 Background Aborts

Memory Protection Unit (MPU) settings must be correct for any region that the CPU is going to access. If the address that the CPU issues falls outside any of the defined regions and the MPU is enabled, the MPU is hard-wired to abort the access. That is, all accesses for an address that is not mapped to a region in the MPU generate a background fault. A background fault does not occur if the background region is enabled and the access is Privileged. An MPU background fault might indicate a stack overflow, and be rectified by allocating more stack.

In the example below, in line 55, an address that falls outside any of the defined regions is trying to be written to.

Example:

void empty_main(void *args)

{

Drivers_open();

Board_driversOpen();

*((volatile uint32_t*) 0xFFFFFFFFF = 0x12;

Board_driversClose();

Drivers_close();

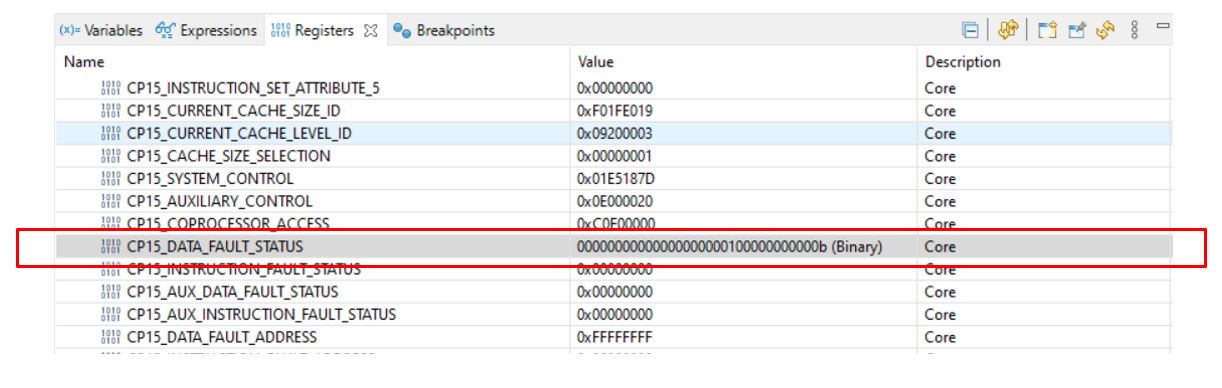

}By checking the DATA_FAULT_STATUS register (DFSR), bits [10, 3:0], you can see that it fits to Background Abort.