SPRAD28 October 2022 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2-Q1 , AM263P4 , AM263P4-Q1 , AM26C31-EP , AM26C31M , AM26C32-EP , AM26C32C , AM26C32M , AM26LS31M , AM26LS32AM , AM26LS33A-SP , AM26LS33AM , AM26LV31E-EP , AM26LV32E-EP , AM26S10 , AM2732 , AM2732-Q1

- Abstract

- Trademarks

- 1 Building for Debug

- 2 Code Composer Studio Stop-Mode Debugging

- 3 Debug Logging

- 4 Multi-Core Debug

- 5 Debugging Arm Cortex-R5 Exceptions

- 6 Debugging Arm Cortex-M4 Exceptions

- 7 Debugging Memory

- 8 Debugging Boot

- 9 Debugging Real-Time Control Loops

- 10E2E Support Forums

9.1.2 How to Use CCS to Capture Trace Data on an AM243x

When having a debug session started for launchpad, the target is connected to CCS and GPIO led blink example for the R5 core is loaded and halted at main.

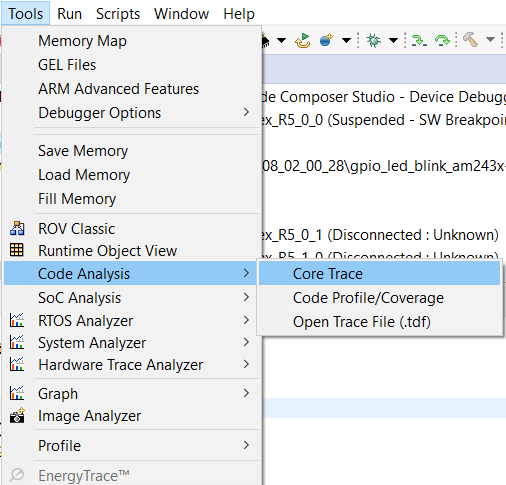

Under the tools → code analysis.

Select the first option (Core Trace) to capture core trace data, which is real-time gathering of instructions being executed by the core.

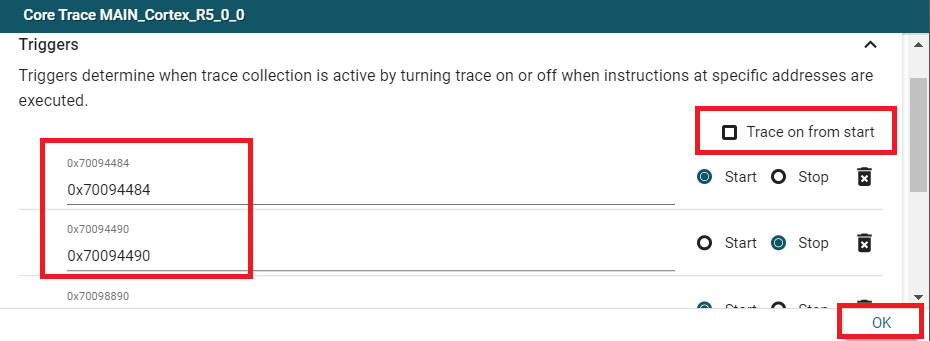

In the core trace tab, there are several options available. Filters are used to include or exclude trace data from specific address ranges. Triggers determine when trace collection is active by turning trace on or off instructions that specific addresses are executed.

Receiver settings allow you to specify the trace receiver to be used to specify the bugger type and specify if trace collection should be synchronized with the target execution. ETB is the only receiver option available for this launchpad (leave the rest of the options as default). Due to the small size of the ETB, it's not possible to capture core trace data for the entire application. Hence, you need to use triggers to enable and disable trace collection at specific addresses. This allows us to only capture the trace data that you are interested without risk of losing any data if the buffer wraps around. Our goal is to enable trace collection only around the part of the toggles the GPIO pin that toggles the LED. You can found those addresses by setting breakpoints and look at the Dissasembly of the breakpoints. Set start and stop addresess, and uncheck the "Trace on from start" option:

Hit on "Ok" and run the program (you can see that the program is running successfully since the led is blinking). Once the program has finished running and the target is halted at the exit point, the captured data in the ETB is sent to CCS and displayed in the core trace view. There you can see the data for each dace entry, data such as program address, the associated opcode and so on.