ZHCSW60B April 2024 – August 2025 IWRL6432AOP

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 功能方框图

- 5 器件比较

- 6 终端配置和功能

-

7 规格

- 7.1 绝对最大额定值

- 7.2 ESD 等级

- 7.3 上电小时数 (POH)

- 7.4 建议运行条件

- 7.5 一次性可编程 (OTP) 电子保险丝的 VPP 规格

- 7.6 电源规格

- 7.7 节电模式

- 7.8 每个电压轨的峰值电流要求

- 7.9 支持的 DFE 特性

- 7.10 射频规格

- 7.11 CPU 规格

- 7.12 热阻特性

- 7.13 天线辐射方向图

- 7.14 天线位置

- 7.15 时序和开关特性

- 8 详细说明

- 9 应用、实施和布局

- 10器件和文档支持

- 11修订历史记录

- 12机械、封装和可订购信息

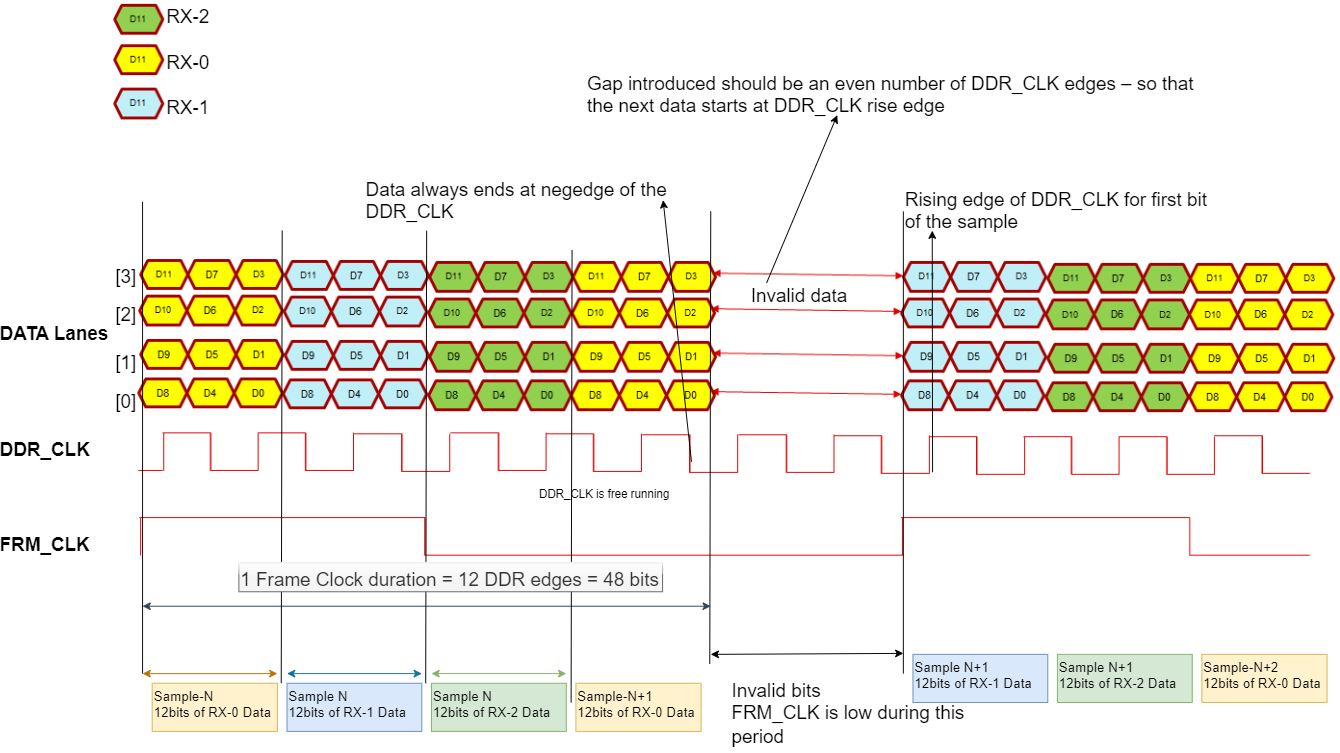

7.15.5.2 RDIF 数据格式

图 7-20 RDIF 数据格式

图 7-20 RDIF 数据格式如上图所示,样本逐个通道发送。一个通道的所有 12 位都在 4 个数据通道上在 3 个 DDR_CLK 边沿发送,接下来是 RX 通道。

帧时钟 (FRM_CLK) 跨 12 个 DDR_CLK 边沿,48 位在 1 个 FRM_CLK 中发送

FRM_CLK 之间可能存在间隙。由于接口速率大于传入速率,因此需间隙

DDR_CLK 是连续的。

DDR_CLK 由 400MHz ADC CLK(ADC CLK 之一)生成 — 为 DFE 选择的速率。它与为 DFE 选择的 400MHz 时钟相同。

新采样始终从 DDR_CLK 的上升沿开始

FRM_CLK 对整个数据位有效,并符合 DDR_CLK 的 Tsu/Th 要求。