ZHCUBD2 April 2023

3.3.3.3 JTAG 连接器

TSW14J59EVM 包含一个业界通用 JTAG 连接器 P2,用于连接到 FPGA 的 JTAG 端口。可以使用该连接器或通过 USB 3.0 接口对 FPGA 进行编程。利用 USB 3.0 接口,可以使用 HSDC Pro 软件 GUI 对 FPGA 进行编程。每次 TSW14J59EVM 下电时,都会删除 FPGA 配置。每次电路板上电后,用户都必须通过 GUI 对 FPGA 进行编程。也可以使用两个板载闪存器件 U3 和 U6 配置 FPGA。

TSW14J59EVM 还具有表面贴装的 Digilent JTAG 编程器 U5,可用于对 FPGA 进行编程。

闪存器件 TSW14J59EVM 包括两个可加载 FPGA 固件的串行闪存编程 EEPROM。跳线 J35 确定当按下开关 SW2 时哪个 EEPROM 会配置 FPGA。如果已对 EEPROM 进行了编程,那么在上电后,如果 J35 在引脚 1-2 之间有分流器,则按下 SW2 会将闪存器件 U3 的内容加载到 FPGA 中。如果分流器位于引脚 2 与 3 之间或已移除,则会使用 U6 的内容对 FPGA 进行编程。

对存储器器件进行编程

要使用新文件对 U3 和 U6 进行编程,请执行以下步骤:

注: 安装 Vivado® 版本 2018.3 或更高版本(实验室版)

- 通过 JTAG Xilinx 编程器电缆将 TSW14J59 采集卡连接到 PC。这是 JTAG 连接 P2。

- 在 JP3 上安装分流器。

- 打开 Vivado 安装:

- 双击 Open Hardware Manager。

- 在“Hardware Manager”中,左键点击 Open target,然后选择 Auto Connect。

- 最后一步会列出通过 JTAG 编程器电缆连接到 PC 的所有 FPGA。

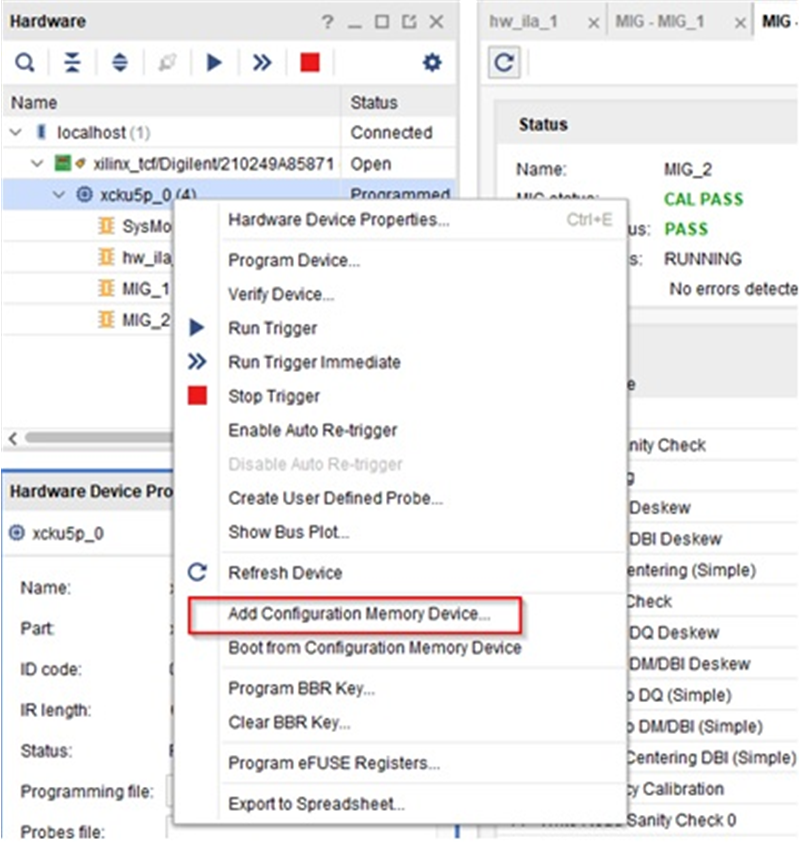

- 右键点击“xcku5p_0”-> 点击 Add Configuration Memory Device。

图 3-1 添加配置存储器器件

图 3-1 添加配置存储器器件 - 在弹出窗口中,搜索“mt25qu256-spi-x1_x2_x4”组件。点击 OK 按钮。

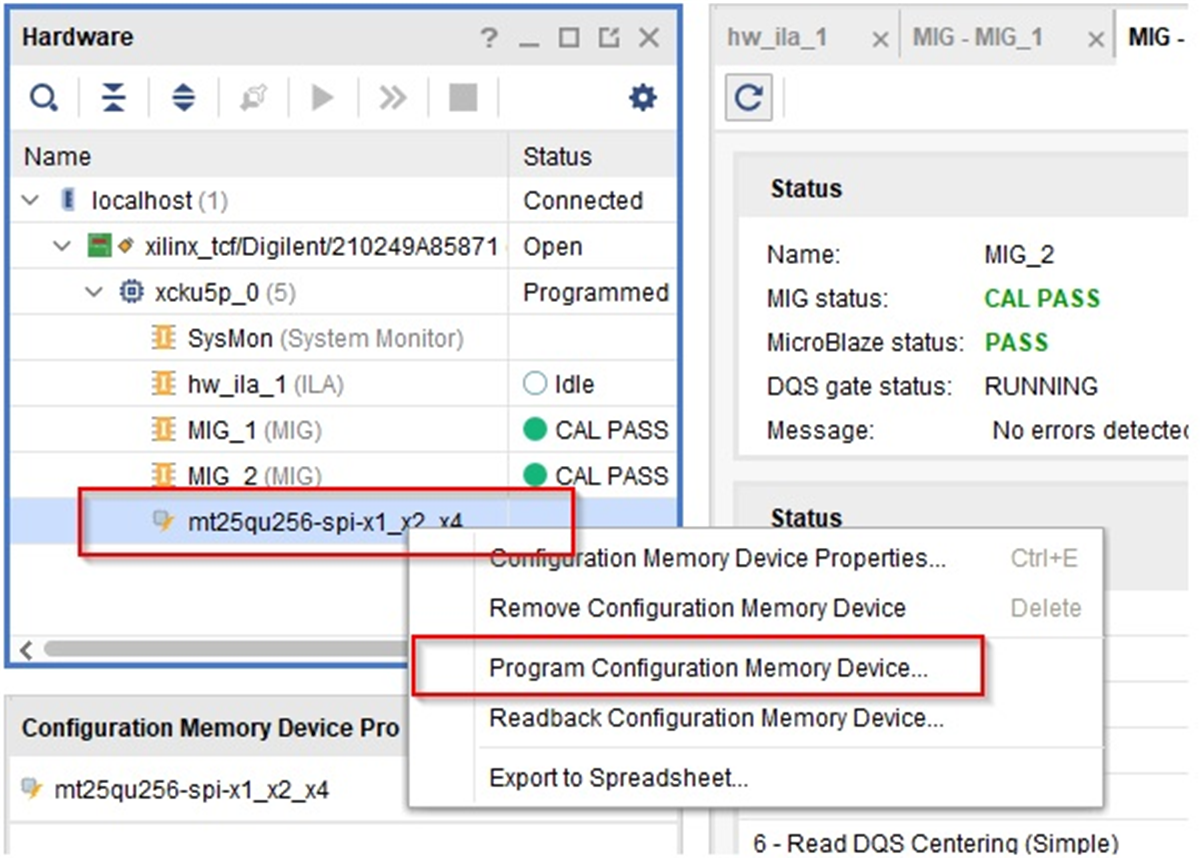

- 右键点击器件“mt25qu256-spi-x1_x2_x4”,然后点击 Program Configuration Memory Device(请参阅图 3-2)。

图 3-2 对存储器器件进行编程

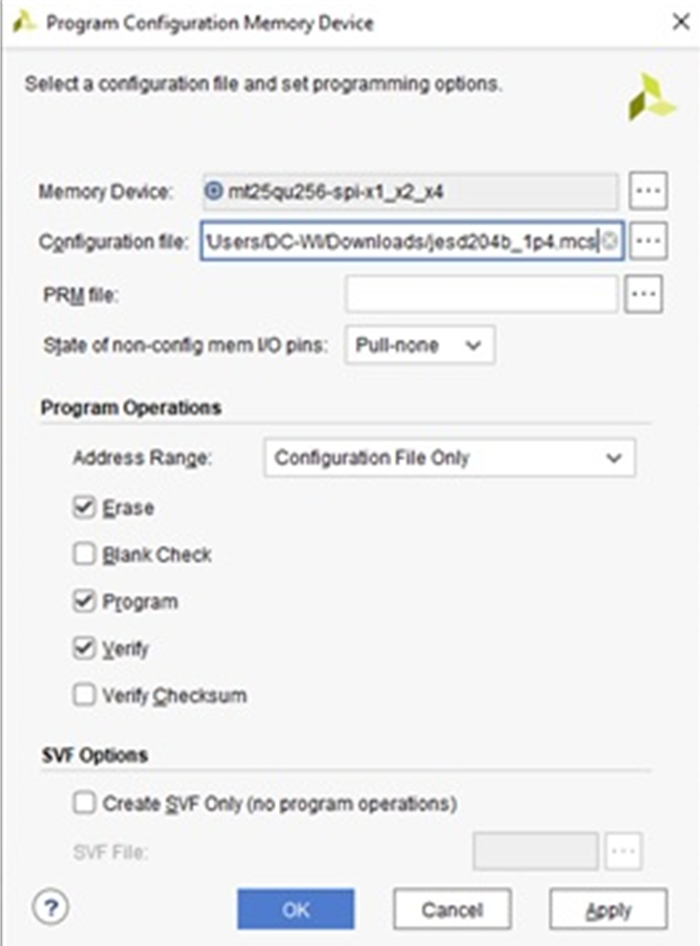

图 3-2 对存储器器件进行编程 - 要对 U3 进行编程,请在 J35 引脚 1 至 2 上插入分流器,打开要加载的新“xx.mcs”文件,并检查编程中的以下设置。完成后,点击 OK 按钮。图 3-3 展示了要加载的配置文件。如果文件加载正确,则会打开一条新消息 Flash programming completed successfully。点击“OK”按钮。

图 3-3 配置文件

图 3-3 配置文件 - 要对 U6 进行编程,请在 J35 的引脚 2 至 3 上放置分流器,打开要加载的新“yy.mcs”文件,并检查编程中的以下设置。完成后,点击 OK 按钮。

- 编程完成后,点击 SW2、FPGA RESET,以将映像加载到 FPGA 中。通过 J35 的引脚 2 至 3 上的分流器,存储在 U6 中的映像被加载到 FPGA 中。通过 J35 的引脚 1 至 2 上的分流器,存储在 U3 中的映像被加载到 FPGA 中。