SPRAC21A June 2016 – June 2019 OMAP-L132 , OMAP-L138 , TDA2E , TDA2EG-17 , TDA2HF , TDA2HG , TDA2HV , TDA2LF , TDA2P-ABZ , TDA2P-ACD , TDA2SA , TDA2SG , TDA2SX , TDA3LA , TDA3LX , TDA3MA , TDA3MD , TDA3MV

-

TDA2xx and TDA2ex Performance

- Trademarks

- 1 SoC Overview

- 2 Cortex-A15

- 3 System Enhanced Direct Memory Access (System EDMA)

- 4 DSP Subsystem EDMA

- 5 Embedded Vision Engine (EVE) Subsystem EDMA

- 6 DSP CPU

- 7 Cortex-M4 (IPU)

- 8 USB IP

- 9 PCIe IP

- 10 IVA-HD IP

- 11 MMC IP

- 12 SATA IP

- 13 GMAC IP

- 14 GPMC IP

- 15 QSPI IP

- 16 Standard Benchmarks

- 17

Error Checking and Correction (ECC)

- 17.1 OCMC ECC Programming

- 17.2 EMIF ECC Programming

- 17.3 EMIF ECC Programming to Starterware Code Mapping

- 17.4 Careabouts of Using EMIF ECC

- 17.5 Impact of ECC on Performance

- 18 DDR3 Interleaved vs Non-Interleaved

- 19 DDR3 vs DDR2 Performance

- 20 Boot Time Profile

- 21 L3 Statistics Collector Programming Model

- 22 Reference

- Revision History

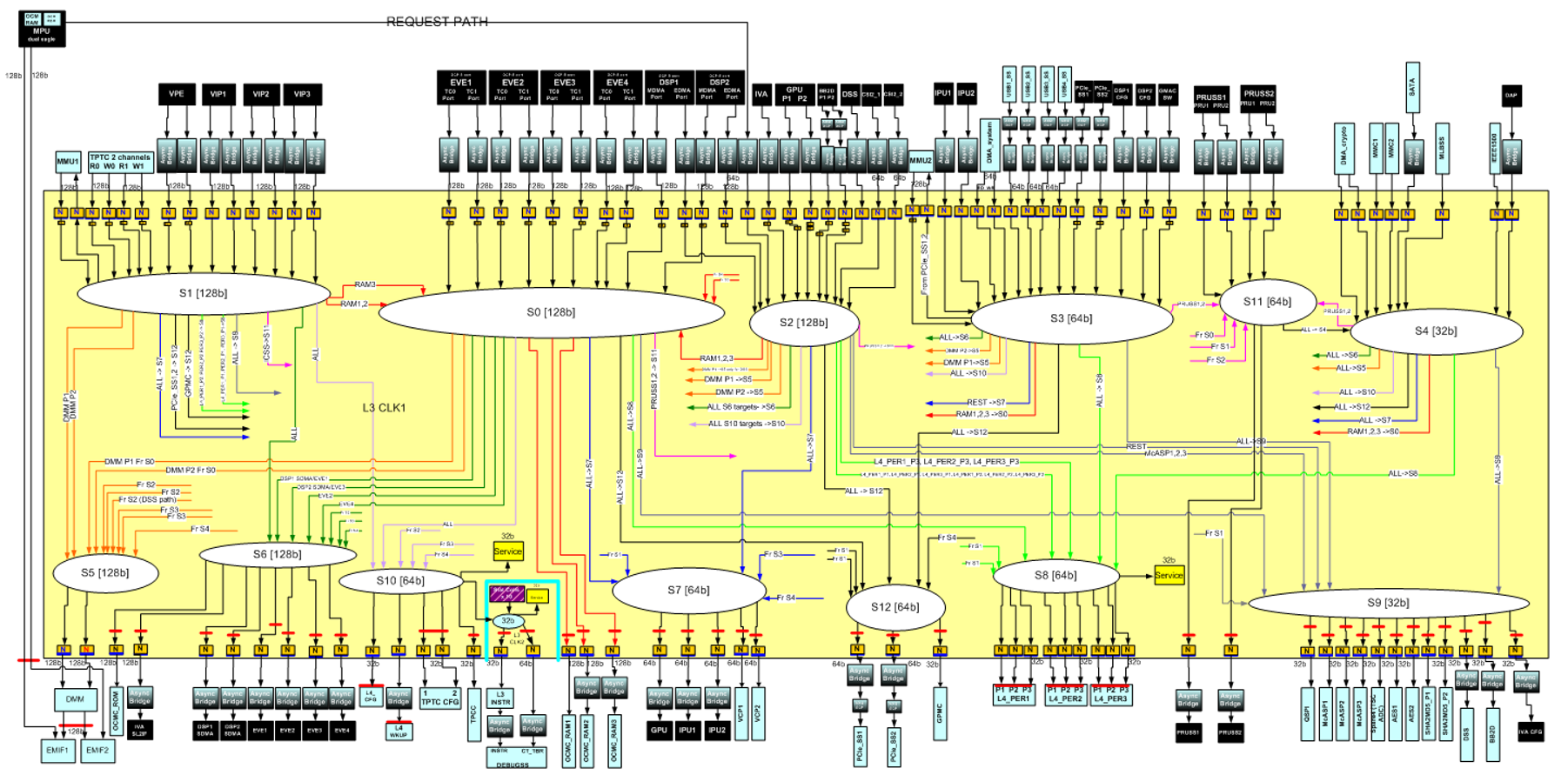

1.3 TDA2xx and TDA2ex System Interconnect

The system’s interconnect and master to slave connection in the TDA2xx and TDA2ex devices is shown in Figure 2. For those initiators and peripherals not supported by TDA2ex, the slave and master ports to L3 are tied to a default value resulting in errors when trying to access a peripheral not present in the device.

Figure 2. TDA2xx and TDA2ex SoC Interconnect Diagram

Figure 2. TDA2xx and TDA2ex SoC Interconnect Diagram Broadly, the list of masters and slaves in the system are listed in Table 2 and Table 3.

Table 2. List of Master Ports in TDA2xx and TDA2ex

| Master | Supported Maximum Tag Number | Maximum Burst Size (Bytes) | Type |

|---|---|---|---|

| MPU | 32 | 120 | RW |

| CS_DAP | 1 | 4 | RW |

| IEEE1500_2_OCP | 1 | 4 | RW |

| DMA_SYSTEM RD | 4 | 128 | RO |

| MMU1 | 33 | 128 | RW |

| DMA_CRYPTO RD | 4 | 124 | RO |

| DMA_CRYPTO WR | 2 | 124 | WR |

| TC1_EDMA RD | 32 | 128 | RO |

| TC2_EDMA RD | 32 | 128 | RO |

| TC1_EDMA WR | 32 | 128 | WR |

| TC2_EDMA WR | 32 | 128 | WR |

| DMA_SYSTEM WR | 2 | 128 | WR |

| DSP1 CFG | 33 | 128 | RW |

| DSP1 DMA | 33 | 128 | RW |

| DSP1 MDMA | 33 | 128 | RW |

| DSP2 CFG (1) | 33 | 128 | RW |

| DSP2 DMA (1) | 33 | 128 | RW |

| DSP2 MDMA (1) | 33 | 128 | RW |

| CSI2_1 | 1 | 128 | WR |

| IPU1 | 8 | 56 | RW |

| IPU2 | 8 | 56 | RW |

| EVE1 P1 (1) | 17 | 128 | RW |

| EVE1 P2 (1) | 17 | 128 | RW |

| EVE2 P1 (1) | 17 | 128 | RW |

| EVE2 P2 (1) | 17 | 128 | RW |

| EVE3 P1 (1) | 17 | 128 | RW |

| EVE3 P2 (1) | 17 | 128 | RW |

| EVE4 P1 (1) | 17 | 128 | RW |

| EVE4 P2 (1) | 17 | 128 | RW |

| PRUSS1 PRU1 | 2 | 128 | RW |

| PRUSS1 PRU2 | 2 | 128 | RW |

| PRUSS2 PRU1 | 2 | 128 | RW |

| PRUSS2 PRU2 | 2 | 128 | RW |

| GMAC_SW | 2 | 128 | RW |

| SATA | 2 | 128 | RW |

| MMC1 | 1 | 124 | RW |

| MMC2 | 1 | 124 | RW |

| USB3_SS | 32 | 128 | RW |

| USB2_SS | 32 | 128 | RW |

| USB2_ULPI_SS1 | 32 | 128 | RW |

| USB2_ULPI_SS2 | 32 | 128 | RW |

| GPU P1 | 16 | 128 | RW |

| MLB | 1 | 124 | RW |

| PCIe_SS1 | 16 | 128 | RW |

| PCIe_SS2 | 16 | 128 | RW |

| MMU2 | 33 | 128 | RW |

| VIP1 P1 | 16 | 128 | RW |

| VIP1 P2 | 16 | 128 | RW |

| VIP2 P1 | 16 | 128 | RW |

| VIP2 P2 | 16 | 128 | RW |

| VIP3 P1 | 16 | 128 | RW |

| VIP3 P2 | 16 | 128 | RW |

| DSS | 16 | 128 | RW |

| GPU P2 | 16 | 128 | RW |

| GRPX2D P1 | 32 | 128 | RW |

| GRPX2D P2 | 32 | 128 | RW |

| VPE P1 | 16 | 128 | RW |

| VPE P2 | 16 | 128 | RW |

| IVA | 16 | 128 | RW |

- Not present in TDA2ex.

Table 3. List of L3 Slaves in TDA2xx and TDA2ex

| Slave | Tag Number | Maximum Burst Size (Bytes) |

|---|---|---|

| GPMC | 1 | 124 |

| GPU | 1 | 8 |

| IVA1 SL2IF | 1 | 16 |

| OCMC_RAM1 | 1 | 128 |

| DSS | 1 | 124 |

| IVA1 CONFIG | 1 | 124 |

| IPU1 | 1 | 56 |

| AES1 | 1 | 4 |

| AES2 | 1 | 4 |

| SHA2MD5_1 | 1 | 4 |

| DMM P1 | 32 | 128 |

| DMM P2 | 32 | 128 |

| L4_WKUP | 1 | 124 |

| IPU2 | 1 | 56 |

| OCMC_RAM2 (1) | 1 | 128 |

| OCMC_RAM3 (1) | 1 | 128 |

| DSP1 SDMA | 1 | 128 |

| DSP2 SDMA (1) | 1 | 128 |

| OCMC_ROM | 1 | 16 |

| TPCC_EDMA | 1 | 128 |

| PCIe SS1 | 1 | 120 |

| VCP1 | 1 | 128 |

| L3_INSTR | 1 | 128 |

| DEBUGSS CT_TBR | 1 | 128 |

| QSPI | 256 | 128 |

| VCP2 | 1 | 128 |

| TC1_EDMA | 1 | 128 |

| TC2_EDMA | 1 | 128 |

| McASP1 | 1 | 128 |

| McASP2 | 1 | 128 |

| McASP3 | 1 | 128 |

| PCIe SS2 | 1 | 120 |

| SPARE_TSC_ADC | 1 | 128 |

| GRPX2D | 1 | 4 |

| EVE1 (1) | 16 | 128 |

| EVE2 (1) | 16 | 128 |

| EVE3 (1) | 16 | 128 |

| EVE4 (1) | 16 | 128 |

| PRUSS1 | 1 | 128 |

| PRUSS2 | 1 | 128 |

| MMU 1 | 32 | 128 |

| MMU 2 | 32 | 128 |

| SHA2MD5_2 | 1 | 4 |

| L4_CFG | 1 | 124 |

| L4_PER1 P1 | 1 | 124 |

| L4_PER1 P2 | 1 | 124 |

| L4_PER1 P3 | 1 | 124 |

| L4_PER2 P1 | 1 | 124 |

| L4_PER2 P2 | 1 | 124 |

| L4_PER2 P3 | 1 | 124 |

| L4_PER3 P1 | 1 | 124 |

| L4_PER3 P2 | 1 | 124 |

| L4_PER3 P3 | 1 | 124 |

- Not present in TDA2ex.

The L3 high-performance interconnect is based on a Network-On-Chip (NoC) interconnect infrastructure. The NoC uses an internal packet-based protocol for forward (read command, write command with data payload) and backward (read response with data payload, write response) transactions. All exposed interfaces of this NoC interconnect, both for Targets and Initiators; comply with the OCP IP2.x reference standard.