SLWU079D March 2012 – April 2016

-

TSW140x High Speed Data Capture/Pattern Generator Card

- Trademarks

- 1 Functionality

- 2 Hardware Configuration

- 3 Software Start up

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW1405 Functional Description

- 7 TSW1406 Functional Description

- 8 Revision History

5.1 Testing a TSW1400 EVM with a DAC3152 EVM

This section describes the pattern generator operation when testing with a DAC3152 EVM that has a LVDS input interface.

- Power down the TSW1400.

- Connect J5 of the DAC3152 to connector J4 of the TSW1400.

- Provide +5 VDC to J12 and return to J13 of the DAC3152 EVM.

- Provide a 0.5-Vrms, 250-MHz clock to J9 of the DAC3152 EVM.

- Power up the TSW1400 EVM

- Start up the HSDC Pro GUI as described in the Software Start Up.

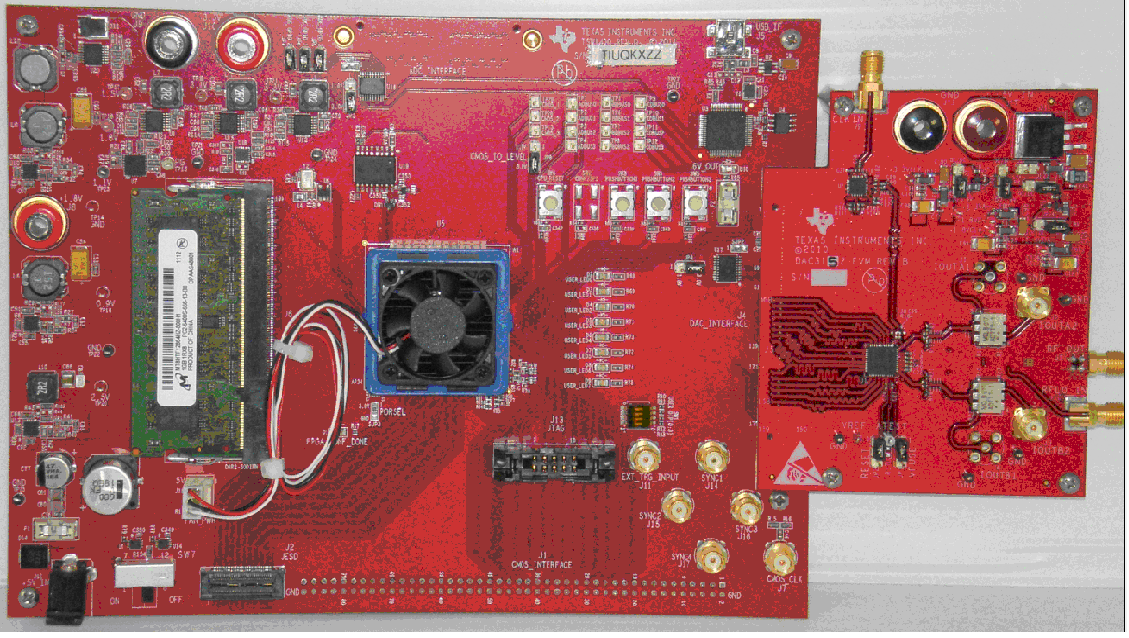

- A TSW1400 EVM connected to a DAC3152 EVM is shown in Figure 12.

Figure 12. TSW1400 EVM Interfacing to a DAC EVM

Figure 12. TSW1400 EVM Interfacing to a DAC EVM NOTE

The FPGA clocks from DAC EVMs to the TSW1400 EVM have to be LVDS level. Exceeding LVDS levels may damage the TSW1400 FPGA.