ZHCSLQ7A April 2025 – October 2025 THS3470

PRODUCTION DATA

7.2.2.2 详细设计过程

使用 THS3470 进行设计时,设计人员需要考虑来自交流(电容)和直流(电阻)负载的总输出电流。THS3470 允许的最大直流电流为 1.5A,但许多应用在器件输出端(电缆、寄生电容、栅极电容等)需要电容负载驱动,这可能会在大 dv/dt 阶跃或大信号正弦波期间产生大交流电流。由于 THS3470 的压摆率非常高,在某些自举条件下为 1kV/us,因此需要特别注意将交流峰值电流加上直流电流限制为 2A,如表 7-3 所示。

| 输出电压 (VPP) | 电阻负载 (Ω) | DC 电流 (mA) | 电容负载 (pF) | 最大压摆率 (V/µs) | 交流峰值电流 (mA) | 交流 + 直流峰值电流 (mA) |

|---|---|---|---|---|---|---|

| ±40 | 开路 | 0 | 300 | 2000 | 600 | 600 |

| ±40 | 开路 | 0 | 1000 | 2000 | 2000 | 2000 |

| ±50 | 开路 | 0 | 300 | 2000 | 600 | 600 |

| ±50 | 开路 | 0 | 1000 | 2000 | 2000 | 2000 |

| ±40 | 100 | ±400 | 300 | 2000 | 600 | 1000 |

| ±40 | 100 | ±400 | 1000 | 1600 | 1600 | 2000 |

| ±50 | 100 | ±500 | 300 | 2000 | 600 | 1100 |

| ±50 | 100 | ±500 | 1000 | 1500 | 1500 | 2000 |

虽然自举设计具有一些优势,例如使用 60V 放大器时的输出范围为 100V,但要了解这种架构,需要考虑一些设计注意事项。该设计的一个主要缺点是,由于电源放大器和信号放大器的单个电源均限制在 3V(无负载),因此每个电源轨的输出余量限制会倍增至 6V。此外,每个放大器的输出余量会随着器件升温而增加,并从输出端提供更大的电流。因此,在重负载条件下,120V 电源会损失约 20V 的余量(VEE 损失 10V,VCC 损失 10V)。设计人员必须注意图 5-33以获取有关余量损失的信息,并估算应用中每个放大器在最坏情况下的结温。

驱动这些重负载时,设计人员必须特别注意器件的最高结温 (150C),并使器件保持在安全工作区内,如节 7.5.1.2 所示。与单个 120V 放大器相比,自举设计的一个优点是该设计将芯片上的功耗在信号放大器和电源放大器之间分配,如图 7-6 所示。在同样的场景下,传统 120V 放大器通常消耗 30W 的功率,因为一个输出级晶体管上必须出现 30V 的压降,而自举设计会在信号和电源放大器之间分配 30W 的功率。由于 THS3470 封装能够以理想的方式拉取 4°C/W,这意味着自举电路在 25°C 的环境温度下可以将总功耗从 30W 增加到 60W。

使用 THS3470 的数字功能时,信号放大器的 DGND 必须连接到 VEE 引脚而非电路板接地,否则在输出信号移动时,THS3470 的数字块可能会超过器件的电源电压范围。同样,对于 VEE 电源放大器,DGND 范围只能在由正电源(本设计中为 0V)供电的 7V 电压下运行。因此,THS3470 的许多数字引脚(P0、P1、OVTEMP_FLAG、ISNK_FLAG、ISRC_FLAG、ISNK_LIMIT_EN、ISRC_LIMIT_EN)必须相对于 DGND 和 VDD 进行连接,以防止器件损坏。在快速瞬变期间读取信号放大器标志的状态需要电平转换电路(差分放大器),因此设计人员可以在禁用电流限制的电源放大器上使用器件标志,以限制电路的复杂性。

要使用自举电路设置电流限制,请使用一个电阻器将 ISRC_LIMIT 连接到 VEE、将 ISNK_LIMIT 连接到 VCC 以将信号放大器电流限制设置为所需的值,并将电源放大器电流限制保留为最大值 (1.35A DC)。如果电源放大器在信号放大器之前进入电流限制,信号放大器可能会损坏。建议不要在信号放大器上使用 IOUT_MONITOR 引脚,因为 VMID 电压会随输出电压变化。如果需要对自举设计进行电流监测,则可以在电源放大器上监测 IOUT_MONITOR。

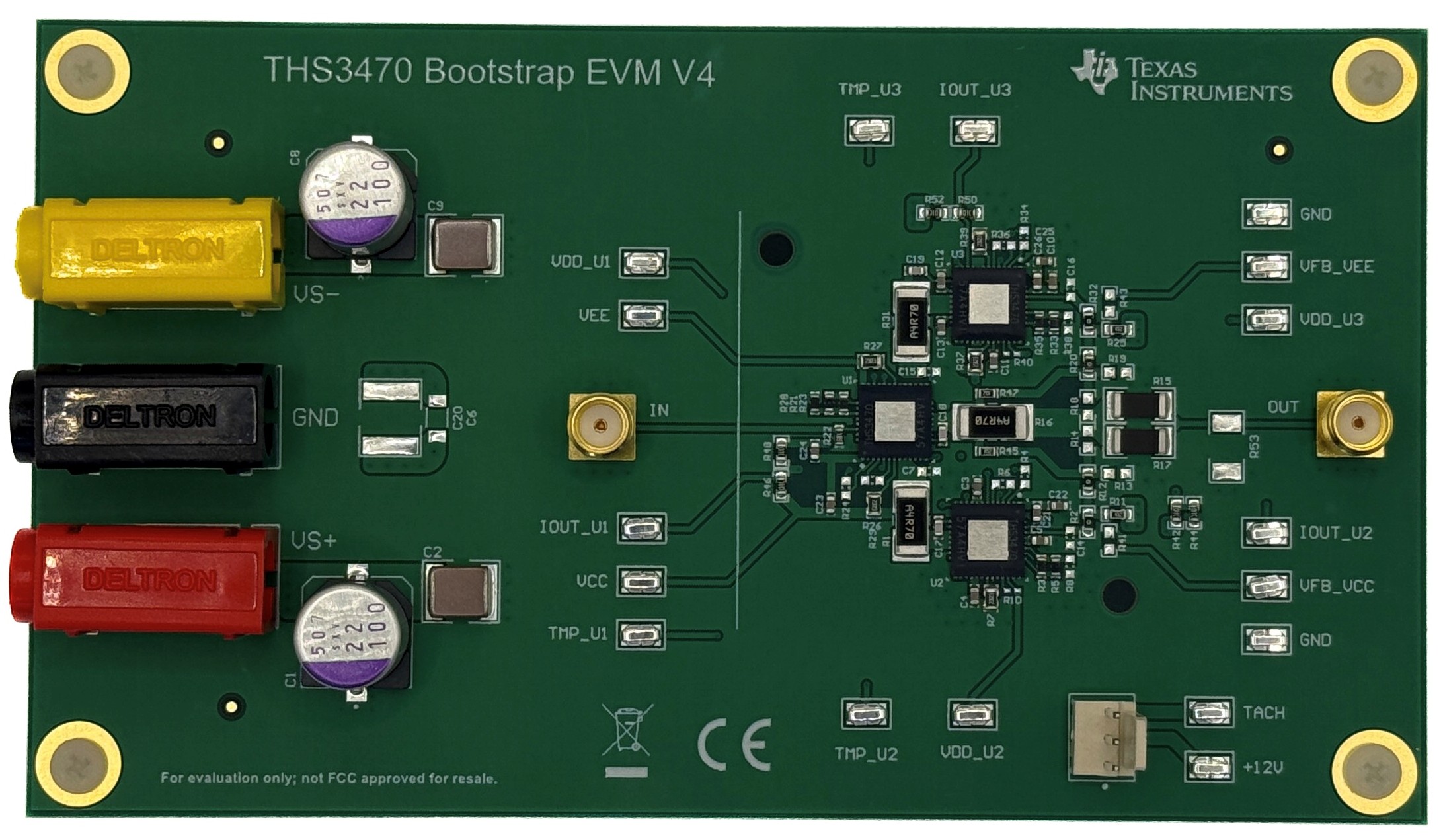

图 7-7 THS3470 自举 PCB

图 7-7 THS3470 自举 PCB