ZHCSOA7D June 2021 – July 2025 BUF802

PRODUCTION DATA

7.4.2 复合环路模式(CL 模式)

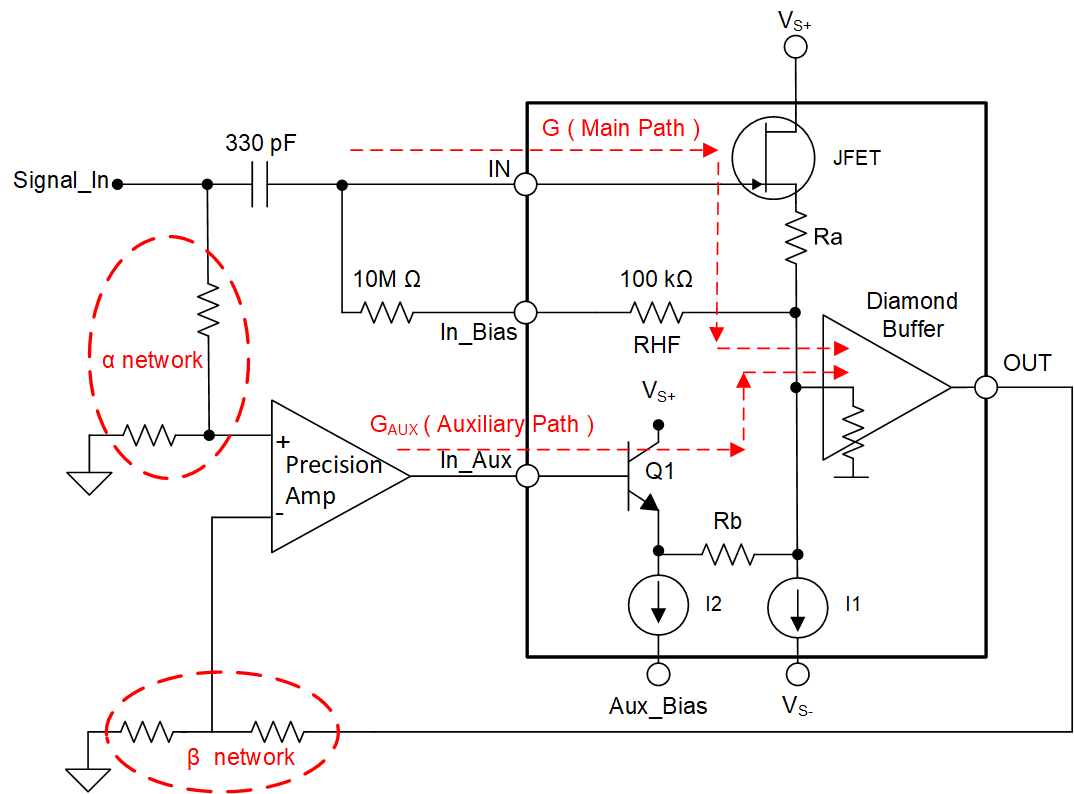

图 7-11 内部原理图 - CL 模式

图 7-11 内部原理图 - CL 模式 图 7-12 CL 模式频率响应

图 7-12 CL 模式频率响应图 7-11 所示的 330pF 输入串联电容器将输入信号分离为低频率和高频率分量。这些信号分别施加到 In_Aux 和 IN。IN 引脚通过主路径控制 BUF802 的输出,而 In_Aux 引脚则通过辅助路径控制输出。

CL 模式 下,复合环路的传递函数可分为以下 3 个频率区域:

- 低频率区域:复合环路在低频率区域的增益为 α/β(由 α 和 β 网络决定)。在低频率区域,330pF 输入电容器在主路径中呈现高阻抗,导致信号通过精密放大器和 In_Aux 引脚流动。该区域的范围从直流到 fLF。fLF 是由精密放大器的增益带宽、辅助路径带宽以及路径中元件的寄生电容共同决定的极点。

- 高频率区域:在高频率区域,精密放大器和辅助路径会耗尽带宽。复合环路在该区域的净增益仅由 BUF802 的主路径增益决定,它以 G 表示。该区域从在 fHF 产生的极点到 BUF802 的 LSBW。fHF 是由 In_Bias 引脚上的 330pF 串联电容器与 10MΩ 电阻共同形成的极点。

- 交叉频率区域:主路径与辅助路径协同工作,共同决定该区域的增益。为了在该区域保持平坦的频率响应,必须满足以下条件:

- α/β = G

- 高频率响应极点 fHF << 低频率极点 fLF