ZHCACT1B September 2022 – November 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P4 , AM263P4-Q1

5.2 OSPI/QSPI 存储器实现

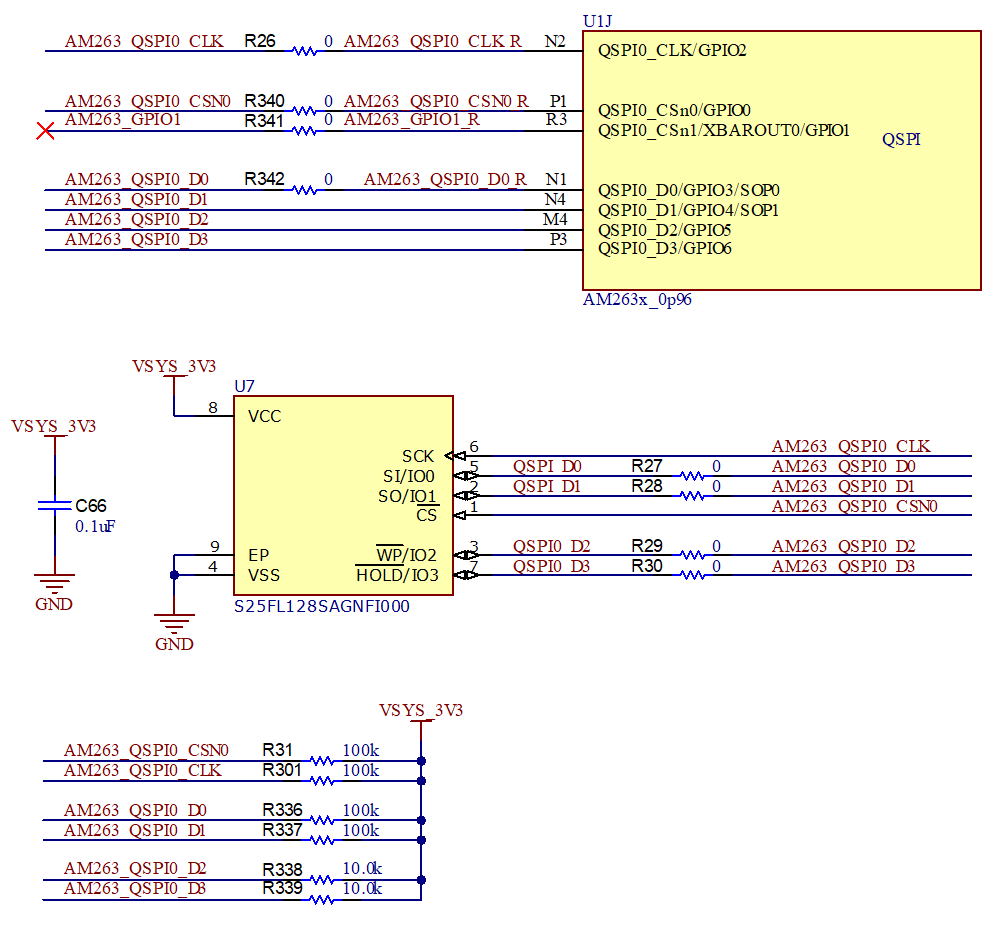

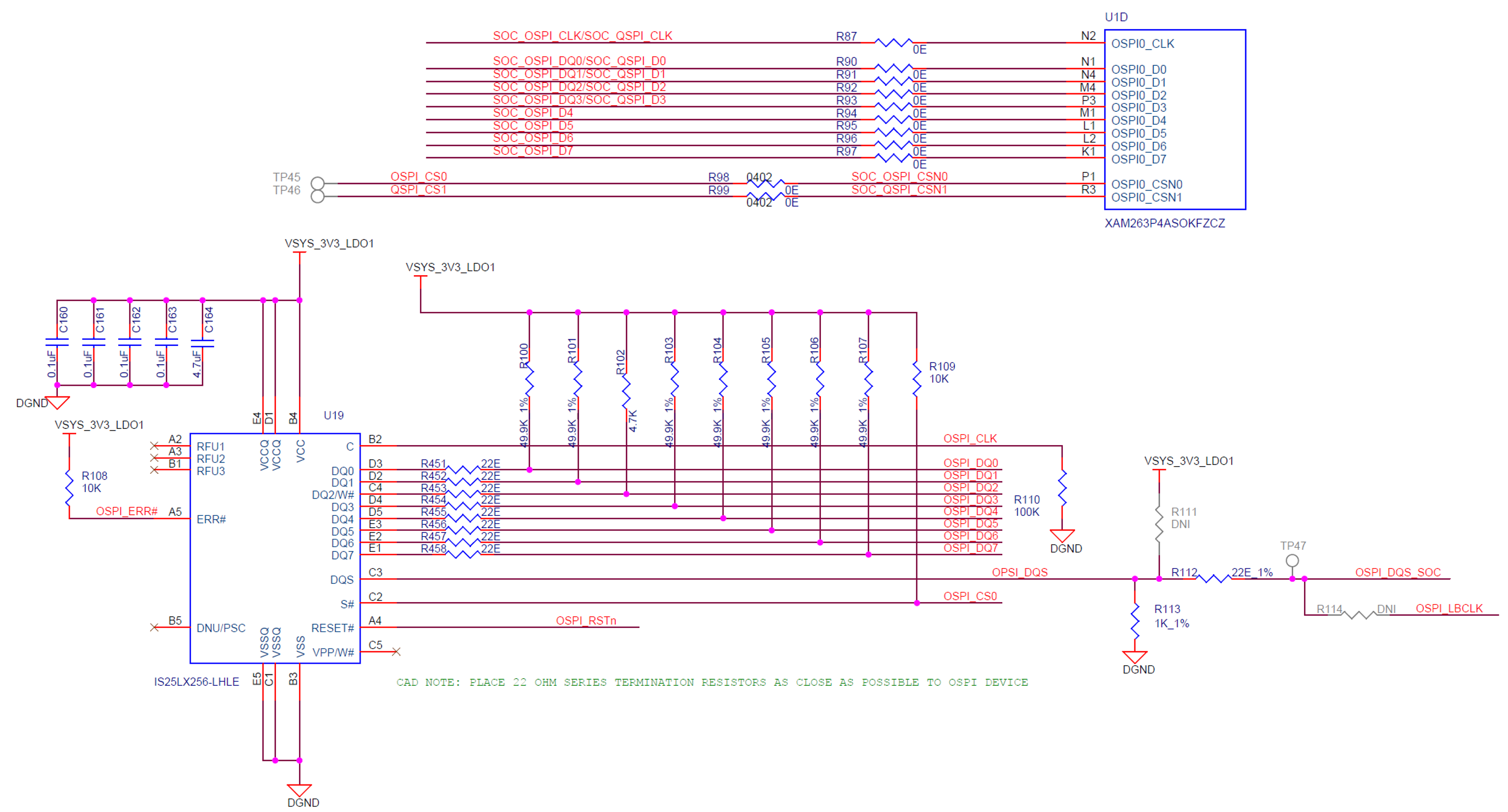

OSPI 闪存存储器接口是 AM263P MCU 的初级引导加载程序存储器位置,QSPI 闪存存储器接口是 AM263x MCU 的初级引导加载程序存储器位置。有关引导 ROM 执行的完整说明,包括 OSPI 和 QSPI 引导信息,请参阅 AM263x Sitara™ 微控制器技术参考手册 和 AM263Px Sitara™ 微控制器技术参考手册。图 5-4 摘录显示了 LP-AM263 LaunchPad 设计中 QSPI NOR 闪存接口的实现。图 5-5 摘录显示了 TMDSCNCD263P AM263Px controlCard 设计中 OSPI NOR 闪存接口的实现。

图 5-4 示例 AM263x QSPI 控制器和 NOR 闪存原理图

图 5-4 示例 AM263x QSPI 控制器和 NOR 闪存原理图 图 5-5 示例 AM263Px OSPI 控制器和 NOR 闪存存储器原理图

图 5-5 示例 AM263Px OSPI 控制器和 NOR 闪存存储器原理图为了控制 OSPI/QSPI 总线转换过冲和下冲,请在 OSPI/QSPI 存储器引脚和 AM263x 或 AM263Px BGA 附近添加以下串联端接电阻器。

- AM263x 或 AM263Px MCU、QSPI0_CLK 的发送侧和 QSPI0_CS[1:0] 上的串联端接

- OSPI0_D[7:0] 或 QSPI0_D[3:0] 的 OSPI/QSPI 存储器侧的串联端接

有关建议的串联终端电阻器放置方式,请参阅图 5-7。

该接口的 OSPI_D[7:1] 和 QSPI_D[3:1] 位用作读取接口,因此使用总线存储器侧的串联端接。OSPI/QSPI_D0 可受益于总线 MCU 侧和 OSPI/QSPI 存储器侧的端接,因为它既用作一位模式写入,又用作一位模式和八/四位模式读取的一部分。但是,从 PCB 布局规划的角度来看,在该总线的两侧放置额外的终端可能很难实现。此处所述的终端方案仅为建议,并非万全之策。有关终端要求的更多详细信息,请参阅节 8。

OSPI/QSPI 时钟、片选和数据线上也需要拉电阻器。在 QSPI 信号上包含以下拉电阻器。根据具体的存储器和应用要求,不同的 QSPI 存储器可能具有不同的上拉/下拉要求。这些拉电阻器建议基于 LP-AM263 设计中使用的 S25FL128x 存储器的实现。要确认所有引脚存储器配置详细信息,请参阅特定于器件的 QSPI 闪存数据表。

- QSPI_CLK、QSPI_CS[1:0] 和 QSPI_D[1:0] - 包含连接至 VDDS33 IO 电源的 100kΩ 上拉电阻器

- QSPI_D[2] - 连接到 VDDS33 IO 电源的 10kΩ 上拉电阻器。这会禁用 S25FL128 闪存上的写保护模式。

- QSPI_D[3] - 连接到 VDDS33 IO 电源的 10kΩ 上拉电阻器。这将禁用 S25FL128 闪存上的保持模式

- OSPI_CLK - 包含连接至 GND 的 100kΩ 下拉电阻器

- OSPI_CS - 连接到 VDDS33 IO 电源的 10kΩ 上拉电阻器

- OSPI_DQS - 1k 下拉至 GND

- OSPI_D[2] - 连接到 VDDS33 IO 电源的 4.7kΩ 上拉电阻器。这会禁用 IS25LX256 闪存存储器上的写保护模式

- OSPI_D[1:0] 和 OSPI_D[7:3] - 49.9kΩ 上拉至 VDDS33 IO 电源

默认情况下,较强的上拉电阻器用于禁用写保护和保持模式。较弱的上拉电阻器用于使线路在事务之间保持有效的逻辑电平。应将拉电阻器放置在靠近 OSPI/QSPI 存储器引脚的位置,以防止形成任何额外的布线残桩。

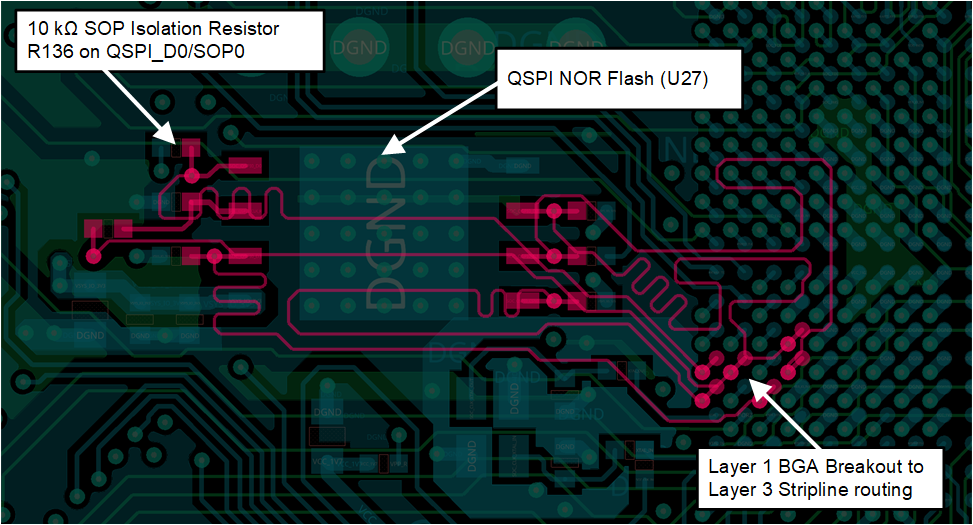

图 5-6 LP-AM263 LaunchPad 布局摘录 – 突出显示 SOP0/QSPI_D0 路径和 SOP 隔离电阻器

图 5-6 LP-AM263 LaunchPad 布局摘录 – 突出显示 SOP0/QSPI_D0 路径和 SOP 隔离电阻器图 5-7 和表 5-2 中提供了 QSPI 存储器接口的附加布线指南。这些指南应用作最大布线延迟和偏斜匹配限制。QSPI 存储器应尽可能靠近 AM263x 或 AM263Px BGA 封装放置。这样布线就可以最大限度地提高延迟裕度和偏斜裕度并最大限度地降低传输线路影响。

图 5-7 AM263x 或 AM263Px QSPI - 路由规则图

图 5-7 AM263x 或 AM263Px QSPI - 路由规则图图 5-8 和表 5-3 中提供了 OSPI 存储器接口的附加布线指南。这些指南应用作最大布线延迟和偏斜匹配限制。OSPI 存储器应尽可能靠近 AM263Px BGA 封装放置。这样布线就可以最大限度地提高延迟裕度和偏斜裕度并最大限度地降低传输线路影响。

图 5-8 AM263Px OSPI - 布线规则图

图 5-8 AM263Px OSPI - 布线规则图| 规格编号 | 规格 | 值 | 单位 |

|---|---|---|---|

| 1 | QSPI_CLK、QSPI_CS0、QSPI_D[3:0] 最大延迟 | 450 | ps |

| 2 | QSPI_CLK 至 QSPI_D[3:0] 最大偏斜 | 50 | ps |

| 3 | 近似最大布线距离 | 3214 | mil |

| 4 | 近似最大布线偏斜 | 357 | mil |

| 5 | 串联终端电阻器(上图中的 R1)应靠近 AM263x 的 QSPI_CLK 发送引脚放置,以控制时钟线路的上升时间和反射。 | 可变,0 到 40 | Ω |

| 6 | 串联端接电阻(上图中的 R2)应靠近所连接存储器的 QSPI 数据引脚放置,以控制数据线路的上升时间和反射。 | 可变,0 到 40 | Ω |

| 规格编号 | 规格 | 值 | 单位 |

|---|---|---|---|

| 1 | OSPI_CLK、OSPI_CS0、OSPI_D[7:0] 最大延迟 | 450 | ps |

| 2 | OSPI_CLK 至 OSPI_D[7:0] 和 OSPI_CSn 最大偏斜 | 60 | ps |

| 3 | OSPI_CLK 至 OSPI_DQS 最大偏斜 | 30 | ps |

| 4 | 近似最大布线距离 | 3214 | mil |

| 5 | OSPI_CLK 至 OSPI_D[7:0] 和 OSPI_CSn 近似最大布线偏斜 | 429 | mil |

| 6 | OSPI_CLK 至 OSPI_DQS 近似最大布线偏斜 | 214 | mil |

| 7 | 串联端接电阻器(上图中的 R1)应靠近 AM263Px 的 OSPI_CLK 发送引脚放置,以控制时钟线路的上升时间和反射。 | 可变,0 到 40 | Ω |

| 8 | 串联端接电阻应靠近所连接存储器和 AM263Px 的 OSPI 数据引脚放置,以控制数据线路的上升时间和反射。 | 可变,0 到 40 | Ω |