ZHCACS0 june 2023 ADC12DJ5200RF , ADC32RF52 , ADC32RF54 , ADC32RF55 , ADC34RF52 , ADC34RF55

3.3 后台校准

后台校准是在 ADC 运行期间进行的连续过程。后台校准涉及连续使用未校准的备用 ADC 内核。校准此备用 ADC 内核后,ADC 内核会与(其中一个)有效 ADC 内核交换。因此,后台校准可在各种环境(例如快速变化的温度)中实时保持 ADC 的精度。但是,后台校准比其他校准模式消耗的功率更多,因为备用 ADC 内核始终处于通电状态,并且正在与有效 ADC 内核进行持续交换。

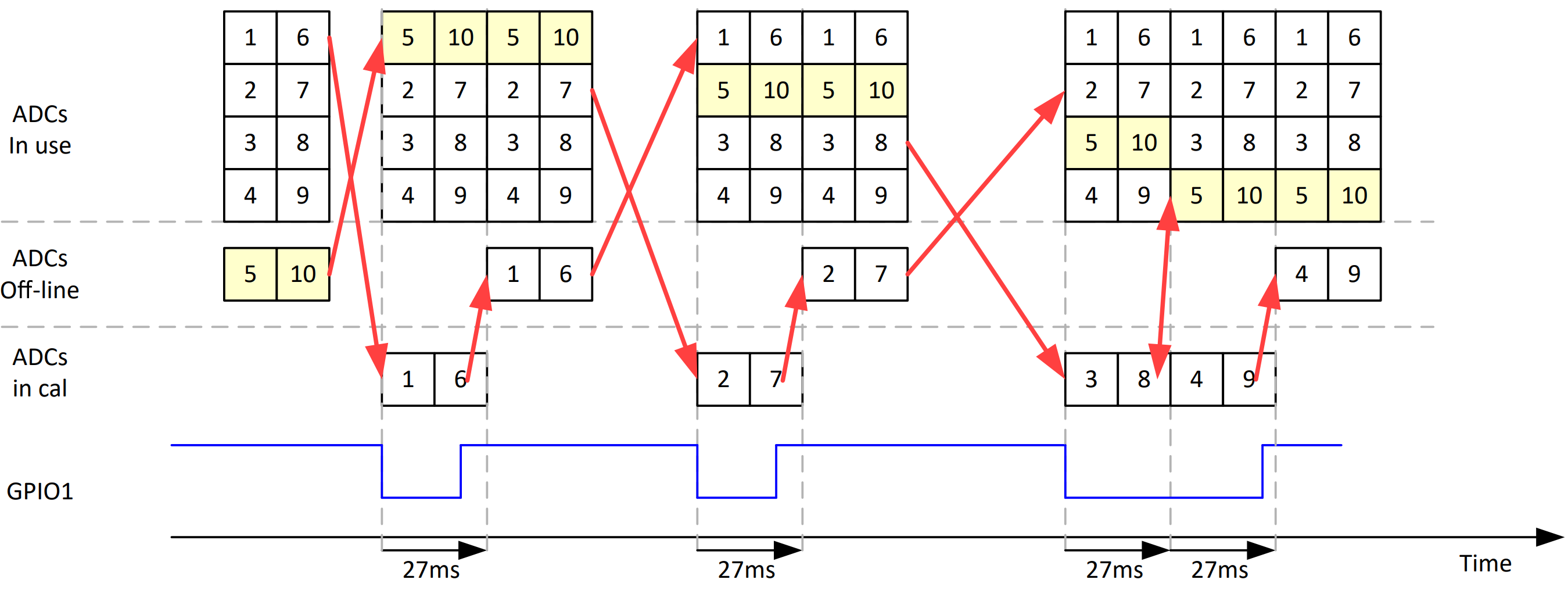

对于 ADC32RF55,后台校准功能在数据表中被称为连续校准。在连续校准期间,五个内部 ADC 内核(每个通道)中的一个大约每 27ms 交换一次,如果器件以 3GSPS 运行,则相当于大约每 8100 万个样本交换一次。图 3-4 比较了前台校准期间的内部 ADC 内核交换(前两个 GPIO1 脉冲表示两个单独的前台校准)与 ADC 内核在连续校准期间的交换方式(较长的 GPIO1 脉冲用于表示连续校准)。

图 3-4 后台校准期间的 ADC32RF55 内核交换

图 3-4 后台校准期间的 ADC32RF55 内核交换必须通过寄存器字段使用 SPI 配置后台校准。某些器件(如 ADC12DJ5200RF)支持低功耗后台校准 (LPBG) 模式(如先前的图 2-1 所示),可降低后台校准期间的总功耗,但会增加器件电源的瞬态要求。在 ADC32RF55 实例中,可将 GPIO 配置为临时冻结后台校准,从而在低活动水平期间降低功率耗散。