ZHCUBK6A May 2018 – December 2023

- 1

- 摘要

- 商标

- 1简介

- 2设备

-

3设置过程

- 3.1 安装 High-Speed Data Converter (HSDC) Pro 软件

- 3.2 安装配置 GUI 软件

- 3.3 连接 EVM 和 TSW14DL3200EVM

- 3.4 将电源连接到电路板(关闭)

- 3.5 将信号发生器连接到 EVM(*在定向之前禁用射频输出)

- 3.6 打开 TSW14DL3200EVM 的电源并连接到 PC

- 3.7 打开 ADC12DLXX00EVM 的 5V 电源并连接到 PC

- 3.8 打开信号发生器射频输出

- 3.9 打开 ADC12DLXX00EVM GUI 并对 ADC 和时钟进行编程

- 3.10 校准 EVM 上的 ADC 器件

- 3.11 打开 HSDC 软件并将 FPGA 图像加载至 TSW14DL3200EVM

- 3.12 使用 HSDC Pro 软件采集数据

- 4器件配置

- A ADC12DL3200EVM 疑难解答

- B 可选 ADC12DL3200EVM 配置

- C 修订历史记录

B 可选 ADC12DL3200EVM 配置

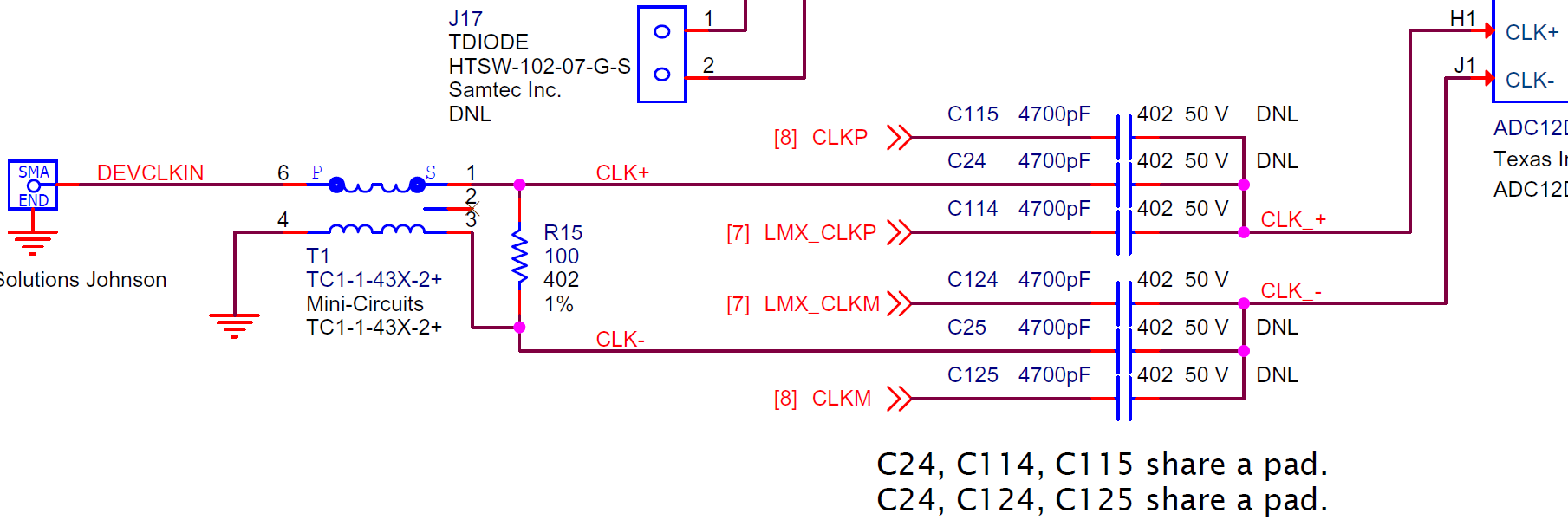

此附录提供了针对可选时钟支持修改 EVM 的设置。

LMK04828 为 LMX2582 提供板载 100MHz VCXO 的缓冲副本。连接可选的 10MHz 基准时钟后,100MHz VCXO 输出频率锁定至 10MHz 基准。此过程可实现对模拟输入信号的相干采样。EVM 可配置为使用外部 ADC 时钟,步骤如下(请参阅图 6-1):

- 修改硬件:

- 移除 C114 和 C124,组装 C24 和 C25。

- 连接信号发生器:

- 将 10MHz 基准从 Sig Gen 1 连接到 Sig Gen 2。

- 配置 Sig Gen 2 以使用来自 Sig Gen 1 的 10MHz 基准输入。

- Sig Gen 1 连接至 DEVCLK (J12)。将发生器频率设置为所需的 FCLK。将输出电平设置为 +9dBm。

- Sig Gen 2 连接到所需的模拟输入,起始点输出电平为 0dBm。

- 对 GUI 进行编程:

- 在 EVM 选项卡中,将时钟源设置为 External。

- 在步骤 2b 中输入 Sampling Frequency (FCLK)。

图 B-1 外部 CLK 配置

图 B-1 外部 CLK 配置ADC12DL3200EVM 包括基准时钟输入 (CLKIN0),允许用户将 LMK04828同步到外部 10MHz 基准,从而实现相干采样

可重新配置 LMX2582 和 LMK04828 以实现更多功能,但此 EVM 并非用作这些器件的完整评估平台。关于完整的评估平台,请参阅 LMK04828 工具文件夹和 LMX2582 工具文件夹。