ZHCABX7A May 2020 – November 2022 TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28033 , TMS320F28033-Q1 , TMS320F28035 , TMS320F28035-EP , TMS320F28035-Q1 , TMS320F28053 , TMS320F28055 , TMS320F2806-Q1 , TMS320F28065 , TMS320F28069 , TMS320F28069-Q1 , TMS320F28069F , TMS320F28069F-Q1 , TMS320F28069M , TMS320F28069M-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.1 跨 C28x/CLA 处理共享资源

使用 CLA 可以有效地从 C28x 卸载控制任务,并在 C2000 器件上实现并发控制环路执行,同时具有前面几节讨论的许多其他优势。但必须注意的是,仍然会在它们之间共享外设,并且对共享寄存器进行并发读取-修改-写入操作会产生数据争用条件,最终导致数据冲突或功能不正确。理想情况下,最好避免 CLA 和 C28x 在运行时同时对同一外设进行任何更新,但如果无法避免,则必须小心处理共享资源的冲突。“cla_ex7_shared_resource_handling”示例说明了这种情况,其中 C28x 和 CLA 以不同频率独立执行对同一 (AQCSFRC) 寄存器的并发读取-修改-写入操作,这会在 C28x 和 CLA 之间产生竞态条件,并可能导致两者其中一个引发的更新丢失或被覆盖。这是一个标准的临界区问题,可以使用互斥等软件握手机制进行处理,但大多数实时控制应用程序对时间敏感,无法承受额外的软件周期开销。此示例建议使用一种基于硬件的替代技术来巧妙地调度 CLA 和 C28x 任务,从而避免对共享资源的访问发生重叠。基于硬件的调度技术利用了 EPWM 模块的可编程相移机制。

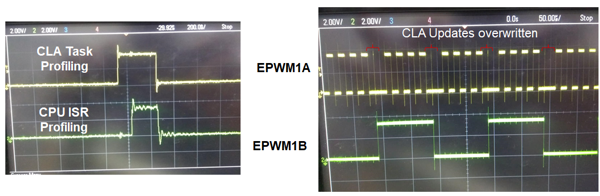

如 图 5-6 所示,C28x ISR 和 CLA 任务分别以 10KHz 和 100KHz 独立运行。C28x ISR 由 EPWM4 周期性触发,并通过软件控制 AQCSFRC 的 CSFB 位来切换 EPWM1B 输出。CLA 任务由 EPWM5 触发,并通过软件控制 AQCSFRC 的 CSFA 位来切换 EPWM1A 输出(请参阅器件 TRM [1] 了解该寄存器的更多详细信息)。因此,在此过程中,C28x 和 CLA 对 AQCSFRC 寄存器执行了重叠的读取-修改-写入操作,如图 5-7 中的分析波形所示。因此,由于 CLA 而对 AQCSFRC 进行的更新会被覆盖,根据从图 5-7 的 EPWM1A 输出波形中观察到的尖峰可以明显看出这一点。

图 5-6 C28x/CLA 的并发读取-修改-写入

图 5-6 C28x/CLA 的并发读取-修改-写入 图 5-7 禁用相移时的分析波形和输出波形

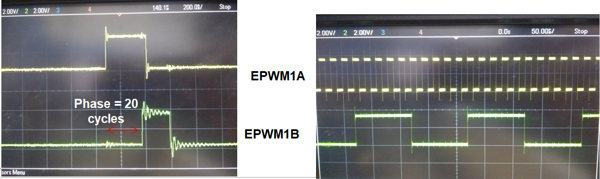

图 5-7 禁用相移时的分析波形和输出波形为解决上述问题,可以使用 EPWM 模块的相移机制(如图 5-8 所示)来高效地调度 CLA 任务和 C28x ISR。EPWM4 在发生每个零事件时生成同步脉冲,并向 EPWM5 提供 20 个周期的相移。这样 CLA 任务和 C28x ISR 都会以原始频率(100KHz 和 10KHz)运行,但 CLA 任务比 C28x ISR 超前 20 个周期的相位偏移,如图 5-9 中的分析波形所示。始终不会发生对 AQCSFRC 进行并发读取-修改-写入操作的情况,EPWM1A 和 EPWM1B 输出的行为方式符合要求,不会出现任何失真,如图 5-9 所示。因此,建议的基于硬件的调度技术有助于避免 C28x 和 CLA 之间的数据竞态条件,还有助于通过避免任何同步访问来实现两个处理引擎的真正并行执行,从而尽可能提高器件的整体性能。

图 5-8 基于 EPWM 的相移技术

图 5-8 基于 EPWM 的相移技术 图 5-9 启用相移时的分析波形和输出波形

图 5-9 启用相移时的分析波形和输出波形