ZHCABX7A May 2020 – November 2022 F28377D-SEP , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28033 , TMS320F28033-Q1 , TMS320F28035 , TMS320F28035-EP , TMS320F28035-Q1 , TMS320F28053 , TMS320F28055 , TMS320F2806-Q1 , TMS320F28065 , TMS320F28069 , TMS320F28069-Q1 , TMS320F28069F , TMS320F28069F-Q1 , TMS320F28069M , TMS320F28069M-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3 CLA 的低中断延迟

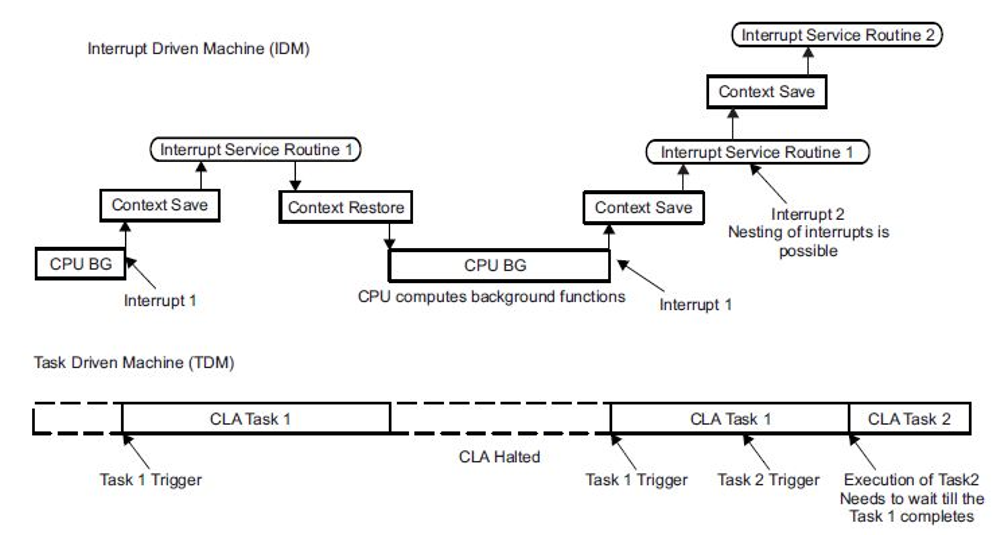

在任何实时控制应用中,采样到输出的延迟(定义为检测、处理和驱动之间经过的时间)是系统的一项重要考虑因素。CLA 的低延迟架构在增加总体系统吞吐量的同时减少了这个采样到输出的时间。之所以可以实现这一点,是因为 CLA 以任务为导向,而非中断驱动状态机,并且不使用中断与硬件同步。相反,该器件支持多达八个独立任务,每个任务都映射到硬件事件,例如计时器,或 ADC 上的数据可用性,等等。在 CLA 上启动的任务会在不涉及任何中断或嵌套的情况下运行至完成,因此不必考虑传统上基于中断的处理器通常涉及到的任何上下文切换开销。所以,CLA 处理数据时几乎没有延迟,最终会降低采样到输出的延迟并实现更快的系统响应。图 3-1 举例说明了任务驱动状态机 (TDM) 和一个中断驱动状态机 (IDM) 间的区别。

图 3-1 中断驱动状态机与任务驱动状态机

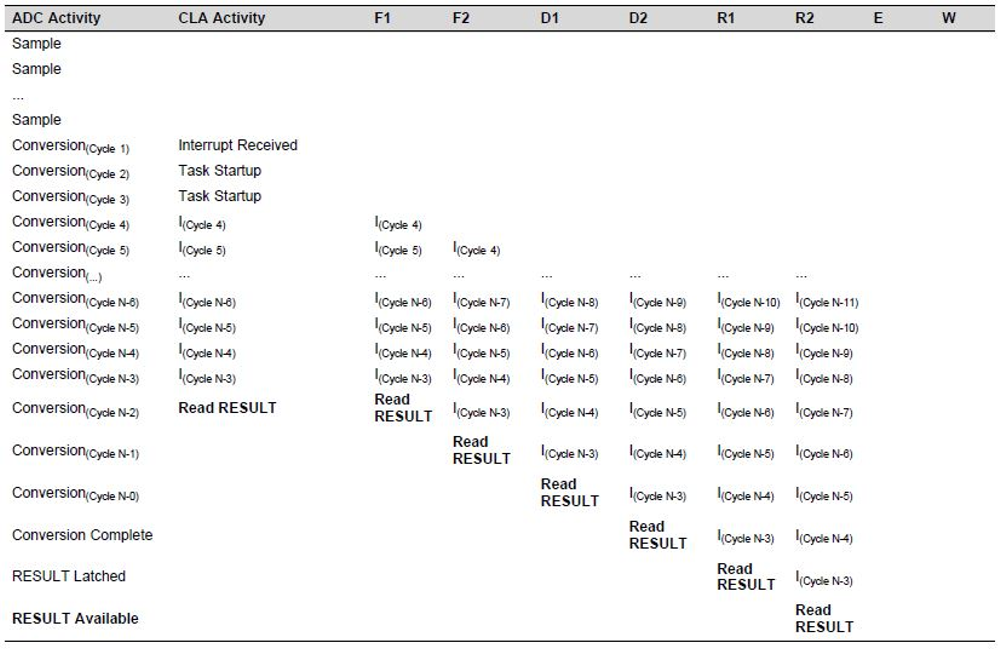

图 3-1 中断驱动状态机与任务驱动状态机CLA 的低中断响应可与 TI 内部 ADC 的提前中断特性结合使用,进一步降低采样到输出的延迟。ADC 可以配置为在转换完成前在采样结束时生成提前中断脉冲。ADC 生成的这个提前中断脉冲可用于触发 CLA 任务,此任务将使得 CLA 能够在 ADC 结果寄存器中有转换结果时立即读取结果。这种即时采样与 CLA 的低中断响应相结合,可实现更快的系统响应和更高频率的控制环路。转换前的可用时间可有效地用于 CLA 任务内任何必要的预处理步骤,如图 3-2 所示。为了实现即时读取,可以根据 N 周期 ADC 转换的 CLA 流水线活动来计算读取请求应该放置在哪条确切指令中。如图 3-3 所示,N-2 指令将即时进入 R2 阶段以读取结果寄存器。对于标准的 12 位 ADC 配置和时钟分频器为 4 的情况,N 为 42。要根据 ADC 的配置确定正确的 N 值,请参阅器件特定的数据表 [4]。

图 3-2 ADC 生成的用于触发 CLA 任务的提前中断

图 3-2 ADC 生成的用于触发 CLA 任务的提前中断 图 3-3 提前中断脉冲的 CLA 流水线活动

图 3-3 提前中断脉冲的 CLA 流水线活动“cla_ex5_adc_just_in_time”示例利用上述概念,即使在非常高的采样频率下也能“即时”读取 ADC 数据。如图 3-4 所示,EPWM1 配置为生成频率为 1MHz 的 PWM 输出信号,该信号也用于在每个周期触发 ADC 采样。该示例还利用了 TI 的 5 类 ADC 中新增的特性,允许根据编程的 OFFSET 值将提前中断脉冲延迟几个周期。因此,ADCA 配置为对通道 0 上的输入进行采样,并在 S/H + 偏移周期结束时生成提前中断。此中断用于触发 CLA 控制任务。该 CLA 任务采用控制逻辑根据读取的 ADC 值更新 PWM 输出的占空比。提前中断特性和 CLA 的低中断延迟搭配使用,使得应用能够执行任何必要的前期工作,以便能够在 ADC 结果可用时立即对其进行处理,并且还能在下一个中断到达之前完成对 PWM 输出的更新。因此,所有三个步骤(采样、处理和驱动)都在 1MHz 周期内完成。如 CLA 任务的以下代码片段所示,为了进行说明,采用了 3 点移动平均滤波器来模拟处理序列,并且在读取 ADC 结果之前执行了少量表示为预处理代码的滤波序列步骤以便利用转换前的可用时间。

图 3-4 “即时”ADC 读取示例展示

图 3-4 “即时”ADC 读取示例展示 //

// Pre-processing for implementing moving average filter, takes 13 cycles

// This is just to illustrate how cycles can be utilized to do some pre-

// processing before ADC result latches.Based on the cycles taken by

// pre-processing code, ADC interrupt offset need to be programmed

//

data_read_total = data_read + data_read_prev;

data_read_prev2 = data_read_prev;

data_read_prev = data_read;

//

// Reading ADC just-in-time

//

data_read = HWREGH(ADCARESULT_BASE + ADC_RESULTx_OFFSET_BASE + ADC_SOC_NUMBER0);

//

// "data_read_total" stores the cumulative sum of current and last 2 data elements

//

data_read_total += data_read;

//

// Taking average of 3 elements, normalizing for 12-bit and mapping to output duty

// linearly in the range 0.1-0.9

// duty = 0.1 + (0.9-0.1) * ((data_read_total / 3) / 2^12 )

//

duty = 0.1f + (data_read_total / (15360.0f));

//

// Writing to the COMPA register for realizing computed duty value

//

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0x1U) = (uint16_t)(duty * EPWM1_PERIOD + 0.5f);ADC 的提前中断 OFFSET 值需要根据预处理所消耗的周期进行调整,以便“即时”读取 ADC 数据。此示例根据示例标头中显示的计算,使用 OFFSET 值 20。下面显示了此 ADC 配置的编程序列。实际用例可能涉及不同的预处理步骤,因此需要相应地对中断 OFFSET 值进行编程。

//

// Set pulse positions to early

//

ADC_setInterruptPulseMode(ADCA_BASE, ADC_PULSE_END_OF_ACQ_WIN);

//

// Set interrupt offset delay as 20 cycles based on the calculation

// shown in example header

//

ADC_setInterruptCycleOffset(ADCA_BASE, 20);