ZHCABL1A December 2020 – January 2022 TAS2563

3 去耦电容器

所有 PCB 布线均已定义阻抗,在各设计阶段都必须考虑这些阻抗。这些信号路径将作为电路板中的附加元件。另外,PCB 线路具有可导致不同功率分布的寄生电感和电容。

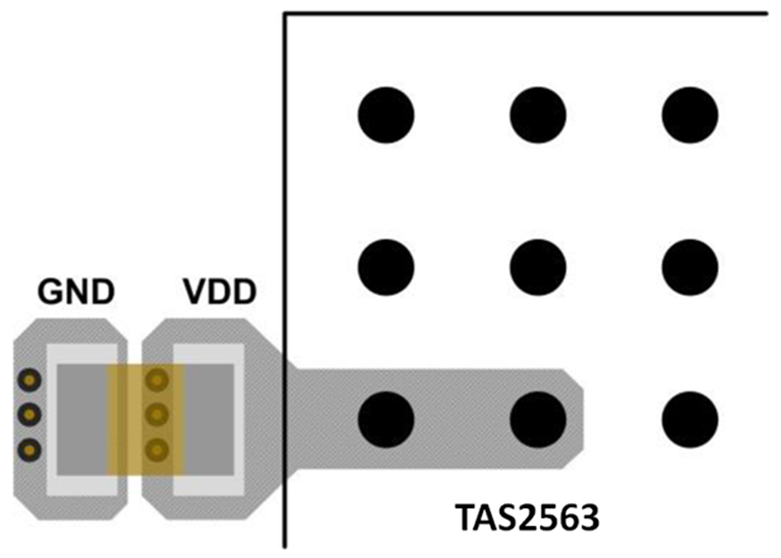

为减少所有这些寄生阻抗的负面影响,TI 建议,VBAT 和 VDD 去耦电容器连接应遵循以下规则:

在同一层且靠近器件引脚的地方放置去耦电容器。去耦电容器存储本地电荷,并在需要时提供较大瞬态电流。TAS2563 器件具有许多开关活动和电压波动,需要在短时间内产生较大电流瞬态。此外,由过孔、迹线和焊盘引起的寄生效应会在电源中产生压降。将去耦电容器靠近电源引脚放置,可补偿这些影响,并在需要时提供较大的瞬态电流。对于多层板,电容器应放置在 TAS2563 器件所在层。否则,因过孔连接而产生的附加电容可能会降低去耦电容值。

将去耦电容器放置在尽可能靠近 VDD 和 GND 过孔的地方。如果可能,将过孔直接放置在电容器安装焊盘上或其附近。过孔定义阻抗取决于其长度和直径。该阻抗可能导致压降(在高频应用中,信号完整性受显著影响)和电流,必须减小或加以避免。因此,TI 建议,在安装焊盘周围增加多个过孔。这种方法可降低寄生阻抗。

图 3-1 去耦电容器

图 3-1 去耦电容器