ZHCABL1A December 2020 – January 2022 TAS2563

1.8 输出引脚

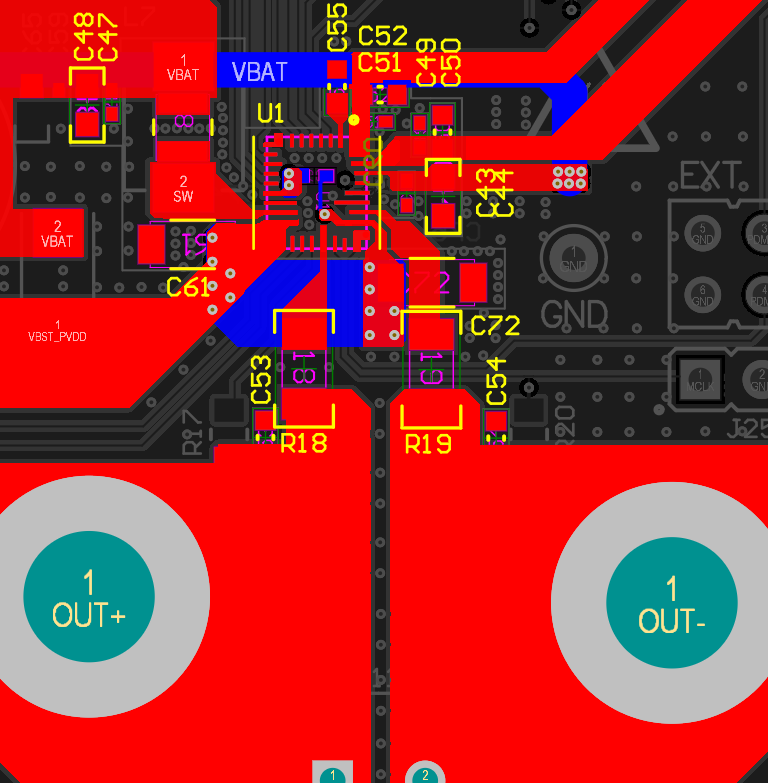

OUT_N 和 OUT_P 分别是 D 类通道的负输出和正输出。由于其开关特性,TI 建议缩短布线,以限制辐射。

为获得理想电流,在输出引脚附近,PCB 迹线必须加宽。此外,需要使用多个过孔在两个层上为输出布线,从而尽可能减少寄生阻抗。

使用 EMI 滤波器(LC 阵列)时,务必考虑以下方面:

首先是滤波器中的电感。

到 GND 或其他输出的电容将拉高电流尖峰,触发过流保护。

TI 建议,将转角频率下限值固定为 1.5MHz,从而简化滤波器的调试和噪声问题。

为 VSNS 引脚串联 1kΩ 电阻器,防止较高的电流尖峰损坏感测引脚的内部结构。

图 1-10 OUT_P 和 OUT_N 连接

图 1-10 OUT_P 和 OUT_N 连接