ZHCAA80B December 2019 – April 2021 AFE7920 , AFE7921 , AFE7988 , AFE7989

5 电源和接地布局方法

AFE79xx EVM 包含以下电源网及关联的接地网。

表 5-1 AFE79xx 电源网及关联的接地返回网

| AFE79xx EVM 通用网名称 | AFE79xx 器件电源引脚 | 网的说明 | 关联的接地网 |

|---|---|---|---|

| VOUT_0p9V | DVDD | 0.9V 数字核心电源网 | DGND |

| VDDT | 0.9V 串行器/解串器数字核心电源网 | ||

| VOUT_1p2V | VDD1p2FB | FB ADC 链使用的 1.2V 电源 | AGND |

| VDD1p2RX | RX ADC 链使用的 1.2V 电源 | ||

| VOUT_1p2VCLK | VDD1p2TXCLK | TX DAC 链时钟使用的 1.2V 电源 | 绑定到 AGND 的虚拟 VSSCLK |

| VDD1p2TXENC | TX DAC 编码器使用的 1.2V 电源 | ||

| VDD1p2PLLRXCML | 将 PLL 时钟分配至 RX ADC 所需使用的 1.2V 电源 | ||

| VDD1p2PLLFBCML | 将 PLL 时钟分配至 FB ADC 所需使用的 1.2V 电源 | ||

| VOUT_1p2V_PLL | VDD1p2PLLCLKREF | PLL 使用的 1.2V 电源 | 绑定到 AGND 的虚拟 VSSCLK |

| PLLA1p8V | VDD1p8PLLVCO | PLL/VCO 使用的 1.8V 电源。这是一个敏感网,在布局时需要格外小心 | 绑定到 AGND 的虚拟 VSSCLK |

| VOUT_1p8V_PLL | VDD1p8PLL | PLL 使用的 1.8V 电源 | 绑定到 AGND 的虚拟 VSSCLK |

| VOUT_1p8V | VDD1p8TX | 1.8V TX DAC 链模拟电源 | AGND |

| VDD1p8RX | 1.8V RX ADC 链模拟电源 | ||

| VDD1p8FB | 1.8V FB ADC 链模拟电源 | ||

| VOUT_1p8V_CLK | VDD1p8RXCLK | 1.8V RX ADC 链时钟电源 | 绑定到 AGND 的虚拟 VSSCLK |

| VDD1p8FBCLK | 1.8V FB ADC 链时钟电源 | ||

| VDD1p8TXDAC | 1.8V TX DAC 链时钟电源 | ||

| VDDA_GPIO_1p8 | VDD1p8GPIO | GPIO 使用的 1.8V 电源 | DGND |

| VDDA1p8 | 串行器/解串器模拟核心 1.8V 电源网 |

以下策略重点介绍了在布置电源网及关联的接地网时需要注意的基本事项。

- 为了提高 PCB 平面对电源平面去耦的有效性,需要减少过孔电感量。敏感电源网必须放置在更靠近器件放置平面的电源层上(即在这个布局设计的顶层附近)。在此设计中,第 3 层和第 5 层包含敏感网,例如:

- VOUT_1p2V

- VOUT_1p2VCLK

- PLLA1p8V

- VOUT_1p8V

- VOUT_1p8V_CLK

- VOUT_1p2V_PLL

- 这些电源轨上的任何噪声干扰都以最小过孔距离从封装到达电源平面。PCB 平面本身具有噪声去耦功能。第 10 层有数字电源 DVDD 和至 PLL 的 1.8V 电源 (VOUT_1P8_PLL)。

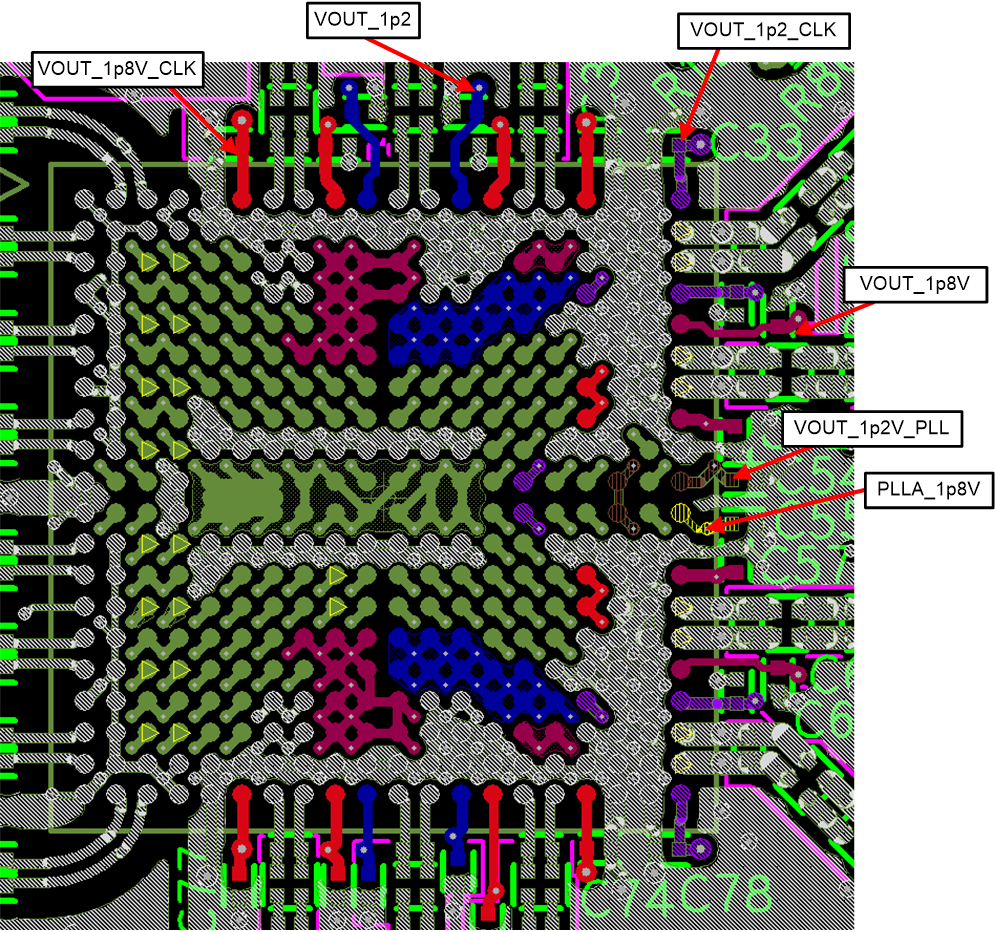

- 图 5-1 突出显示了在器件边沿附近有引脚分配的电源网。用户可以将这些网直接路由至器件同一层上的去耦电容器。此方法不需要在电源网布线时使用任何过孔。

红色:VOUT_1P8_CLK 蓝色:VOUT_1P2 紫色:VOU_1P2_CLK 品红色:VOUT_1P8V 绿色:VOUT_1P2_PLL 黄色:PLLA_1P8V图 5-1 AFE79xx 模拟电源网直接布线至去耦电容器

红色:VOUT_1P8_CLK 蓝色:VOUT_1P2 紫色:VOU_1P2_CLK 品红色:VOUT_1P8V 绿色:VOUT_1P2_PLL 黄色:PLLA_1P8V图 5-1 AFE79xx 模拟电源网直接布线至去耦电容器 - 图 5-2图 5-1 是一个简化示意图,显示了 AFE79xx 的电源引脚名称和对应的 PCB 网名称,以及如 所示的实际物理布局的相对去耦路径连接。

图 5-2 电源网有效去耦

图 5-2 电源网有效去耦 - 图 5-3图 5-1 突出显示了与图 5-2 和 中所示高亮电源网相对应的敏感模拟电源网。

图 5-3 与 AFE79xx 引脚图相对应的敏感模拟电源网

图 5-3 与 AFE79xx 引脚图相对应的敏感模拟电源网 - 数字电源平面 VOUT_0p9V(DVDD 和 VDDT)放在第 10 层(底层之前的最后一个电源层)上。这样就可以让数字电源平面在到达位于底部的去耦电容器时,以最短过孔距离从第 10 层到达底层,实现更好的去耦。

- 电源平面必须避免彼此重叠,以更大限度地减少平面间耦合。在此设计中,AFE79xx 电源平面主要占据第 3 层、第 5 层和第 10 层。在各电源层之间提供的接地层可将电源层与其他干扰源隔离开来。接地层还起到防止电源层噪声泄漏到其他敏感层的作用。例如,DVDD 数字电源平面会成为其他信号层和其他电源层的干扰源。此外,电源平面放置在或“夹在”接地平面之间可实现更好的高频噪声去耦。电源平面层和接地平面层之间的电介质材料发挥去耦电容的重要作用,消除了去耦电容的大部分寄生电感效应。因此,这种“夹层”方法提高了电源噪声去耦的整体性能。图 5-4有效电容取决于电介质的覆盖面积、两个导体之间的距离以及电介质材料的性能,如 中所示。

图 5-4 PCB 电介质材料的有效电容

图 5-4 PCB 电介质材料的有效电容 - 利用铁氧体磁珠或馈通电容器可在使用同一电源平面向器件馈电的电源之间实现隔离。图 5-5在这种情况下,旁路电容器将被放置在电源、铁氧体磁珠和负载(AFE79xx 电源轨)之间,如 中所示。

图 5-5 适合分隔电源轨的铁氧体磁珠和旁路电容器的典型放置方式

图 5-5 适合分隔电源轨的铁氧体磁珠和旁路电容器的典型放置方式