ZHCAA80B December 2019 – April 2021 AFE7920 , AFE7921 , AFE7988 , AFE7989

8 射频布置常规方法:

- 为了更好地隔离射频信号,PCB 设计人员可以交错布置射频输入和射频输出。例如,将 RX A 和 RX C 放置在顶层,将 RX B 和 RX D 放置在底层。

图 8-1 示例 AFE79xx 信号放置策略

图 8-1 示例 AFE79xx 信号放置策略 - 在此设计中,所有射频输入和输出均置于同一层,以便展示在信号路由中使用最少过孔时的典型隔离性能。

- 采用阻抗受控布局模式的射频接地层紧跟在顶层之后并先于底层被插入。

- 差分射频布线必须布置为 100Ω CPWG(具有较低接地平面的共面波导)或微带。RXADC 和 FBADC 的 100Ω 布线为 100Ω 差分至平衡-非平衡变压器,然后 50Ω 单端传输路线为从平衡-非平衡变压器至 SMA 连接器。TXDAC 输出布置为基于 50Ω 的 CPWG,从 TXDAC 输出至平衡-非平衡变压器,然后 50Ω 单端传输路线为从平衡-非平衡变压器至 SMA 连接器。

- 在两个电源层之间插入电源地线。这是为了在电源网彼此重叠时最大限度地减少电源网耦合。图 8-2例如,第 4 层是电源地线,它被插入在第 3 层和第 5 层电源层之间,如 中所示。表 3-1有关堆叠信息,请参阅 。

图 8-2 AFE79xx 堆叠和接地隔离层

图 8-2 AFE79xx 堆叠和接地隔离层 - CLKp/m 输入必须布置在离 TX 输出最远的一层,并通过阻抗受控的过孔转至 CLKp/m BGA 焊球。由于使用过孔是不可避免的,TI 建议仅使用一个差分过孔路由以从器件布置层(顶层或底层)转换到中间层。将 CLKp/m 输入布置在底层,将 TX 输出布置在顶层,这样有助于在 CLK 和 TX 之间实现尽可能大的间隔。如果有任何 TX 泄漏到 CLK 路径,则会使 TX 的谐波失真性能降低。

- 如果串行器/解串器对未布置在顶层/底层,则 TI 建议借助盲孔或背钻孔触及顶层的 BGA 焊珠。这样做的主要目的是避免信号线路上出现残桩。

- TX 布线准则:

- TXDAC 输出默认具有 50Ω 内部终端。来自 TX 的布线的差分阻抗为 50Ω,布置为基于 50Ω 的 CPWG。偏置网络被放置在底层,带有紧缩射频扼流圈和旁路电容器,并且可将偏置网络视作集总元件网络。

- TXDAC 输出需要一个匹配网络,以便使输出阻抗匹配到 50Ω 或 100Ω。基于 50Ω 的匹配通常形成一种更宽的带宽匹配。但在原则上,通过更改匹配网络元件值,用户也可以将其匹配到 100Ω。默认情况下,内部终端必须按 50Ω 阻抗进行设置。TX 输出匹配网络设计策略如下所列:

- TXDAC 内部终端应保持 50Ω 的阻抗,以便实现出色的电力输送和性能。

- 放置匹配网络,以在 AFE79xx TX 输出引脚附近使输出阻抗匹配到 50Ω 或 100Ω。若要实现 50Ω 至 100Ω 阻抗匹配则需采用匹配变换设计技术。

- 检查输出功率和性能。

- 如果由于系统要求而需要增大输出功率,则可以将 TX 输出终端的匹配阻抗更改为 100Ω。输出功率将增加约 2dB,但会以 IMD3 和 APCR 性能下降为代价。

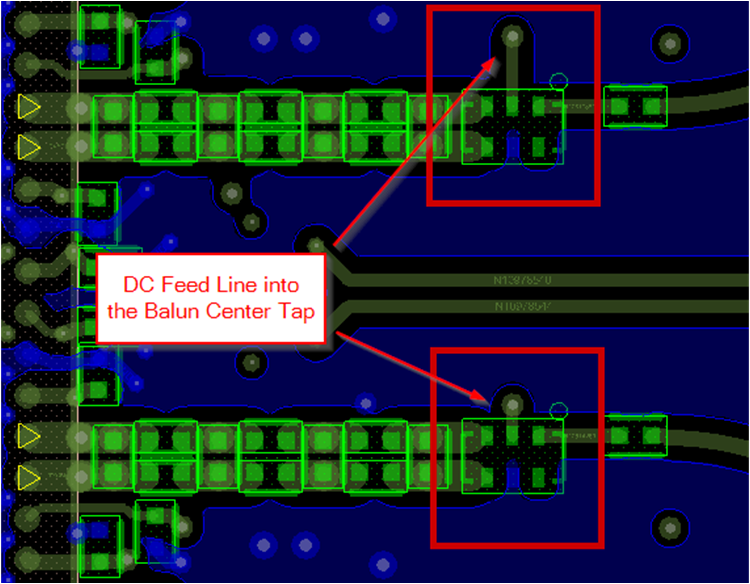

- 变压器中心偏置:直流偏置路由到平衡-非平衡变压器的中心抽头引脚(直流偏置引脚)可能会在某些频段匹配中引起一些共振。目前,对于 TXDAC 输出而言,电感器扼流圈的作用是使 TXDAC 输出偏置,同时将中心抽头引脚接地。TI 建议严格遵循制造商的直流馈电指南,以最大限度地减少直流馈线谐振。

- 下面是横向比较:图 8-3 是具有最小谐振的一个示例。在 TXDAC 侧使用射频扼流圈,以使 DAC 偏置,同时将平衡-非平衡变压器的中心抽头引脚接地。这是目前推荐使用的方法。图 8-4 是使用平衡-非平衡变压器的直流馈线的一个示例。直流线路导致在匹配时出现一些谐振。

图 8-3 之前实施的方案:直流馈线进入平衡-非平衡变压器的中心抽头

图 8-3 之前实施的方案:直流馈线进入平衡-非平衡变压器的中心抽头 图 8-4 当前实施的方案:直流馈线直接接地。通过射频扼流圈提供偏置

图 8-4 当前实施的方案:直流馈线直接接地。通过射频扼流圈提供偏置

- 为获得更好的 RXADC 和 FBADC 噪声系数性能,TI 建议避免使用 STX1 和 STX8 串行器/解串器通道。如果使用了这两个 STX 通道,则 2RX 和 4RX ADC 输入上的噪声频谱密度 (NSD) 性能会略微下降。使用 JESD204 通道多路复用器有助于减少 STX1 和 STX8 串行器/解串器通道的使用,以下是 STX 路由示例。

- 如果 STX 通道数小于六条,请避免使用 STX1 和 STX8 通道,并将 JESD204 输出分配到 STX2、STX3、STX4、STX5、STX6 和 STX7。

- 如果仅需要四条 STX 通道,则将 JESD204 输出分配到 STX3、STX4、STX5 和 STX6。

- 如果仅需要两条 STX 通道,则将 JESD204 输出分配到 STX3 和 STX4。

- 断电编程寄存器与一组中的两条 STX 通道相连。例如,STX1 和 STX2 共享一个断电寄存器,STX3 和 STX4 共享一个断电寄存器。同样,一组中的四条 STX 通道均使用同一个通用串行器/解串器 PLL。例如,STX1、STX2、STX3 和 STX4 使用一个串行器/解串器 PLL,而 STX5、STX6、STX7 和 STX8 使用另一个串行器/解串器 PLL。在规划 STX 映射时,请考虑这个可节省功耗的功能。

- 如果 JESD204 模式需要全部八条 STX 通道处于激活状态,则无法避免会使用 STX1 和 STX8 通道。

- 在布局的最终阶段,执行以下步骤:

- 通过接地修补和接地过孔来修补射频和串行器/解串器布线周围的接地层。

- 去除没有接地过孔的接地覆铜小贴片,避免连接到悬空接地。