ZHCAA38E August 2021 – January 2023 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.2.2 硬件控制

- 测试条件

器件 1 发送数据 -> 器件 2 在接收数据时还将其传递到器件 3 -> 器件 3 在接收数据时还将其传递到器件 1 -> 器件 1 接收数据并验证它是否与最初发送的 Tx 数据匹配。

- 测试案例

8 个字的数据长度,1 条数据线,TXCLK = 30MHz,启用设置 ④(表 5-1)。

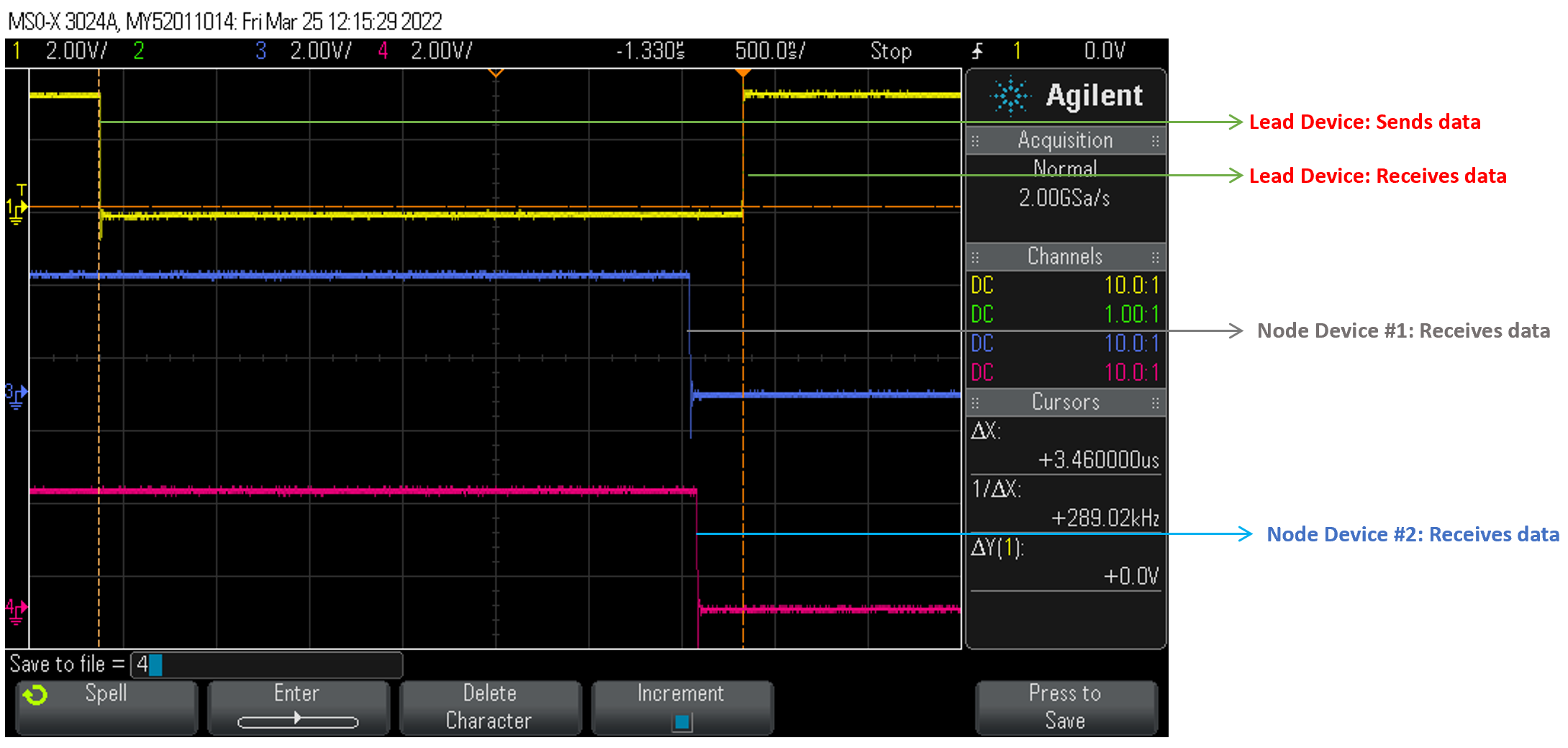

在测试中,当通信期间发生特定事件时,会在软件内翻转 GPIO,并使用示波器对其进行测量以获取相应的时序数据。在下图中,黄色信号表示器件 1(主控器件)的 GPIO 翻转,蓝色信号表示器件 2(节点器件)的 GPIO 翻转,品红色信号表示器件 3(节点器件)的 GPIO 翻转。

图 5-11 三个器件之间采用硬件控制的 FSI 通信

图 5-11 三个器件之间采用硬件控制的 FSI 通信如#GUID-6248909B-E96C-4317-8DA7-D8E1543FA566 所示,对于这种情况,完成三器件菊花链环路所需的数据传输时间为 3.46µs。从图中可看出,器件 2 和器件 3 几乎同时接收数据。另请注意,器件 1 收到数据包时,甚至早于它对数据包传输后生成的 TX 帧中断完成服务,因此,即使接收数据包的时间要早很多,GPIO 翻转仍会延迟。

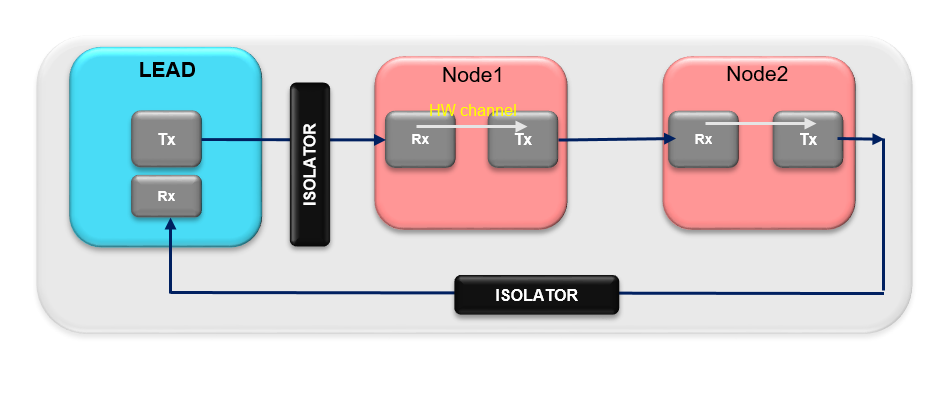

图 5-12 用于生成硬件控制结果的三节点设置

图 5-12 用于生成硬件控制结果的三节点设置请注意,这些结果是在假设器件 2 和器件 3 未相互隔离的情况下生成的。仅器件 1 保留隔离器。所使用的设置如#GUID-0347A809-AC99-441A-8381-1B98C091865A 所示。这是因为每个隔离器都会累积信号失真效应,而这会导致通信错误。

- 由于硬件控制使用硬件中的直通连接,因此网络中的所有器件实际上都连接在一起。这使得无法在硬件中对信号执行任何调节。

- 在硬件控制模式下,隔离器和其他电路对 FSI 时钟和数据线的信号失真效应很明显,特别是,当三个或更多隔离器件在网络中以菊花链形式连接时,可能无法以高于 30MHz 的频率进行通信。为了在较高工作频率下尽可能提高吞吐量,建议采用 DMA 和硬件控制传输模式组合。

表 5-5中给出了更多测试结果。

| FSITXCLK (MHz) | 数据线路数 | 数据长度(16 位字) | 数据通过一个器件的时间 (µs) | 实现完整连接环路的时间 - 3 个器件 (us) | |

|---|---|---|---|---|---|

| CPU 控件 | 50 | 1 | 8 | 7.1 | 16.2 |

| 50 | 1 | 16 | 11.8 | 26.8 | |

| 30 | 1 | 8 | 7.3 | 17.65 | |

| 30 | 1 | 16 | 12.2 | 29.66 | |

| 30 | 2 | 8 | 6.04 | 14.02 | |

| 30 | 2 | 16 | 9.95 | 22.587 | |

| DMA 控件 | 50 | 1 | 8 | 2.3 | 6.5 |

| 50 | 1 | 16 | 4.0 | 11.8 | |

| 30 | 1 | 8 | 3.45 | 9.9 | |

| 30 | 1 | 16 | 5.9 | 17.3 | |

| 30 | 2 | 8 | 2.3 | 6.3 | |

| 30 | 2 | 16 | 3.75 | 10.65 | |

| 硬件控制 | 30 | 1 | 8 | ~0.1 | 3.46 |

| 30 | 1 | 16 | ~0.1 | 5.6 | |

| 30 | 2 | 8 | ~0.1 | 2.26 | |

| 30 | 2 | 16 | ~0.1 | 3.33 |

由于菊花链连接的性质,数据将需要通过许多器件才能从第一个器件传输到最后一个器件。因此,为了降低延迟,务必使每个器件中的数据处理和转发时间尽可能短,尤其是在连接环路中有多个器件时。根据GUID-24B2B5E9-2F63-450E-A220-C3042D39855E.html#GUID-24B2B5E9-2F63-450E-A220-C3042D39855E中得出的结论,为了避免 CPU 使用过多的带宽来移动数据,建议使用 DMA 或硬件直通特性来满足 FSI 通信需求。