ZHCAA38E August 2021 – January 2023 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.2.2.1.1 CPU/DMA 控制

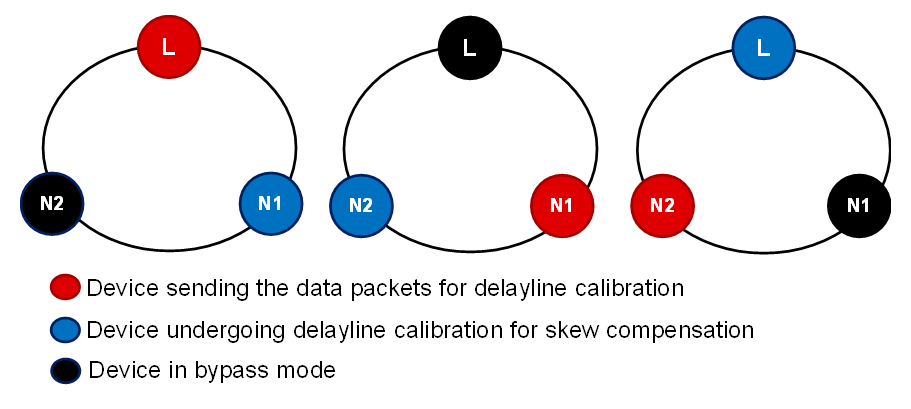

器件 2 延迟线校准:器件 1 使用分配的 ID 调用器件 2,一旦器件 2 收到校准调用,就会使用器件 1 发送的数据包来校准其延迟线。在旁路模式下,器件 3 使用 CPU 控制将从器件 2 收到的数据包传输到器件 1。

器件 3 延迟线校准:器件 2 使用分配的 ID 调用器件 3,一旦器件 3 收到校准调用,就会使用器件 2 发送的数据包来校准其延迟线。在旁路模式下,器件 1 使用 CPU 控制将从器件 3 收到的数据包传输到器件 2。

器件 1 延迟线校准:器件 3 使用分配的 ID 调用器件 1,一旦器件 1 收到校准调用,就会使用器件 3 发送的数据包来校准其延迟线。在旁路模式下,器件 2 使用 CPU 控制将从器件 1 收到的数据包传输到器件 3。

因此,如图 #GUID-E22E87E8-CE4D-4068-B671-1086DD5BAAF5 所示,所有三个器件会分阶段进行校准,到校准结束时,菊花链中所有器件的 Rx 延迟线均会配置适当的值。

图 5-13 CPU、DMA 控制下偏斜补偿的延迟线校准图

图 5-13 CPU、DMA 控制下偏斜补偿的延迟线校准图