SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

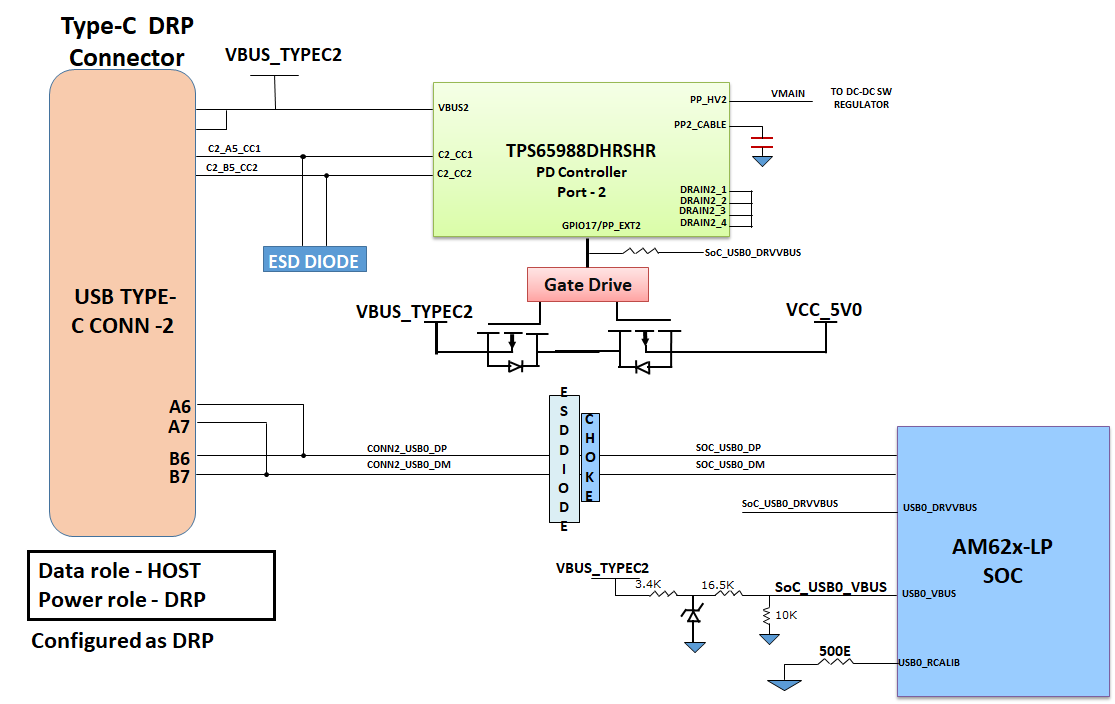

3.5.10.2 USB 2.0 Type C Interface

On AM62x-Low Power SK EVM, USB 2.0 Interface is offered through USB Type-C Connector J15 Mfr part# 2012670005 which supports data rate up to 480Mbps. J15 is used for Data communication and also as power connector. It is configured as a DRP port using PD controller TPS65988DHRSHR IC. So it can act as either Host or Device. Role of the port depends on the type of the device getting connected on the connector and its ability to either sink or source. When the port is acting as DFP, it can source up to 5V@500mA.

USB2.0 Data lines DP and DM from J15 are connected to the USB0 interface of AM62X LOW POWER SoC via choke and ESD protection device. USB0_VBUS to the SOC is provided through a resistor divider network.

A common mode choke of Mfr Part# DLW21SZ900HQ2B is provided on USB Data lines to take care of EMI/ EMC. An ESD protection device of part number ESD122DMXR is included to dissipate ESD strikes on USB2.0 DP/DM Signals. An ESD protection device of part number TPD1E01B04DPLT is included on CC signals and TVS2200DRVR IC is included on VBUS rail of Type-C Connector J15 to dissipate ESD strikes.

Figure 3-17 USB2.0 Type C Interface Block Diagram

Figure 3-17 USB2.0 Type C Interface Block Diagram