SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

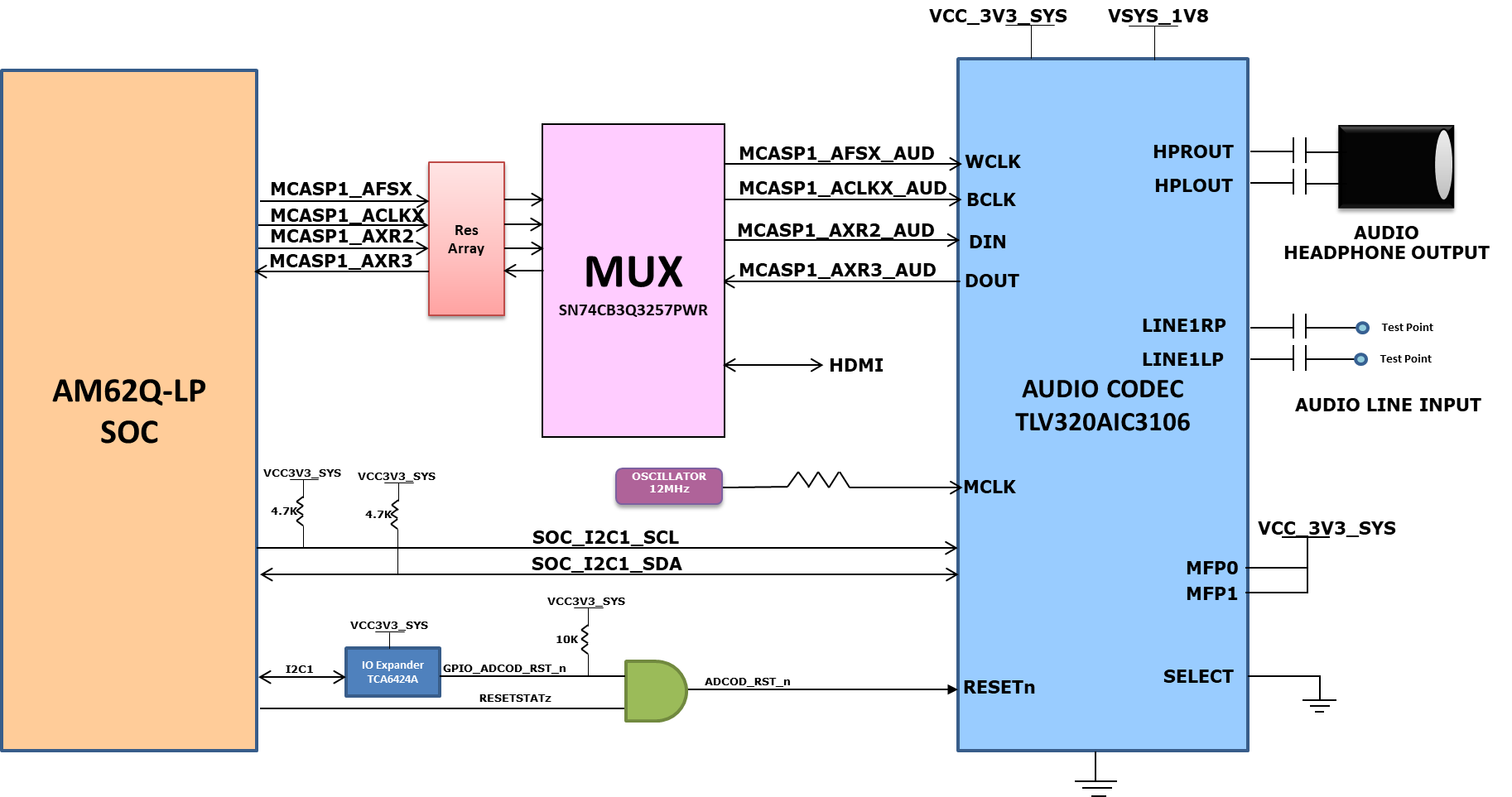

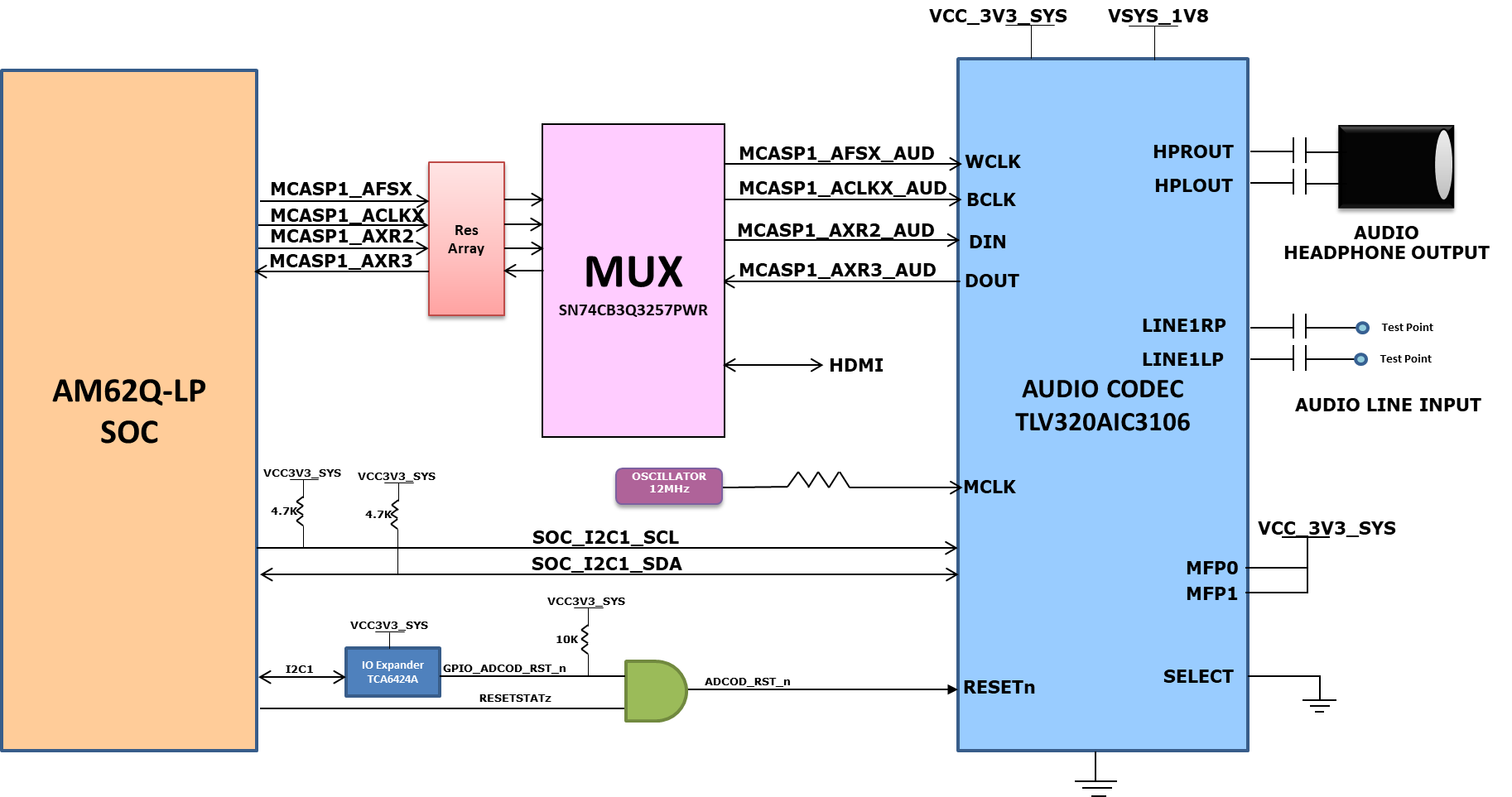

3.5.5 Audio Codec Interface

AM62x-Low Power SK EVM uses TI‘s Low-Power TLV320AIC3106 Stereo

Audio Codec to interface with AM62x via McASP. TLV320AIC3106 is a low-power stereo audio

codec with stereo headphone amplifier, as well as multiple inputs and outputs

programmable in single ended or fully differential configurations. The record path of

the TLV320AIC3106 contains integrated microphone bias, digitally controlled stereo

microphone preamplifier and Automatic gain control (AGC) with mix/Mux capability among

the multiple analog inputs. The stereo audio DAC supports sampling rates from 8 kHz to

96 kHz. 1x Standard 3.5mm TRRS Audio Jack connector Mfr. Part# SJ-43514 shall be

provided for MIC and Headphone output. Audio Codec’s Line inputs are terminated to Test

points. SELECT pin shall be held LOW to select I2C as control interface. Codec can be

configured over I2C interface, where I2C address can be set by driving pins MFP0 and

MFP1 pin either high or low. Both these pins are set to high, so the Device address is

set to 0x1B. Unused inputs and outputs of the Audio Codec are connected to ground. The

Controller Clock input, MCLK to the Audio Codec is provided through a 12.288MHz

Oscillator. Audio serial data bus bit clock BCLK of the codec is driven by the AM62x SoC

through a buffer. Audio serial data bus input and output DIN, DOUT are connected to

SoC’s MCASP1_AXR0 and MCASP1_AXR2 through buffers. An AND output of RESETSTATz and a

GPIO sourced via IO expander are used to reset the Audio codec. The TLV320AIC3106 is

powered by an analog supply of 3.3 V, a digital core supply of 1.8 V, and a digital I/O

supply 3.3 V.

Figure 3-11 Audio Codec Interface Block

Diagram

Figure 3-11 Audio Codec Interface Block

Diagram

Figure 3-11 Audio Codec Interface Block

Diagram

Figure 3-11 Audio Codec Interface Block

Diagram