SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

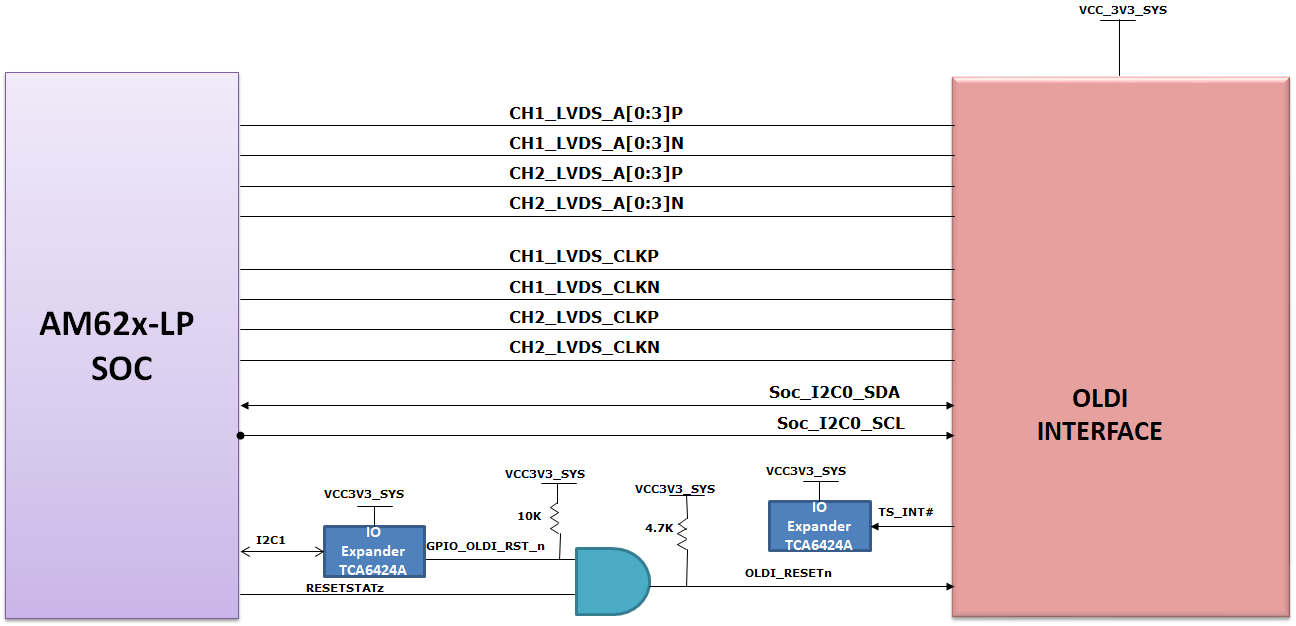

3.5.3 OLDI Display Interface

The OLDI0 Display interface of the AM62x 17x17 SoC is connected to 40 pin LVDS display connector (J22) Mfr Part # FFC2A32-40-T from GCT. The OLDI Interface supports dual channel 8 bit LVDS output. The Pin-out details of the Display connector/ are given in the table below.

Figure 3-9 OLDI Interface Block

Diagram

Figure 3-9 OLDI Interface Block

DiagramTable 3-4 Display Connector Pinout

| Pin no. | Signal | Pin no. | Signal |

|---|---|---|---|

| 1 | VCC_3V3_SYS(EEPROM_VDD) | 21 | CH1_LVDS_A2P |

| 2 | SoC_I2C0_SCL | 22 | GND |

| 3 | SoC_I2C0_SDA | 23 | CH1_LVDS_A3N |

| 4 | NC | 24 | CH1_LVDS_A3P |

| 5 | NC | 25 | GND |

| 6 | GND | 26 | CH2_LVDS_A0N |

| 7 | GND | 27 | CH2_LVDS_A0P |

| 8 | OLDI_RESETn | 28 | GND |

| 9 | GPIO_OLDI_INT | 29 | CH2_LVDS_A1N |

| 10 | GND | 30 | CH2_LVDS_A1P |

| 11 | CH1_LVDS_A0N | 31 | GND |

| 12 | CH1_LVDS_A0P | 32 | CH2_LVDS_CLKN |

| 13 | GND | 33 | CH2_LVDS_CLKP |

| 14 | CH1_LVDS_A1N | 34 | GND |

| 15 | CH1_LVDS_A1P | 35 | CH2_LVDS_A2N |

| 16 | GND | 36 | CH2_LVDS_A2P |

| 17 | CH1_LVDS_CLKN | 37 | GND |

| 18 | CH1_LVDS_CLKP | 38 | CH2_LVDS_A3N |

| 19 | GND | 39 | CH2_LVDS_A3P |

| 20 | CH1_LVDS_A2N | 40 | GND |