SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

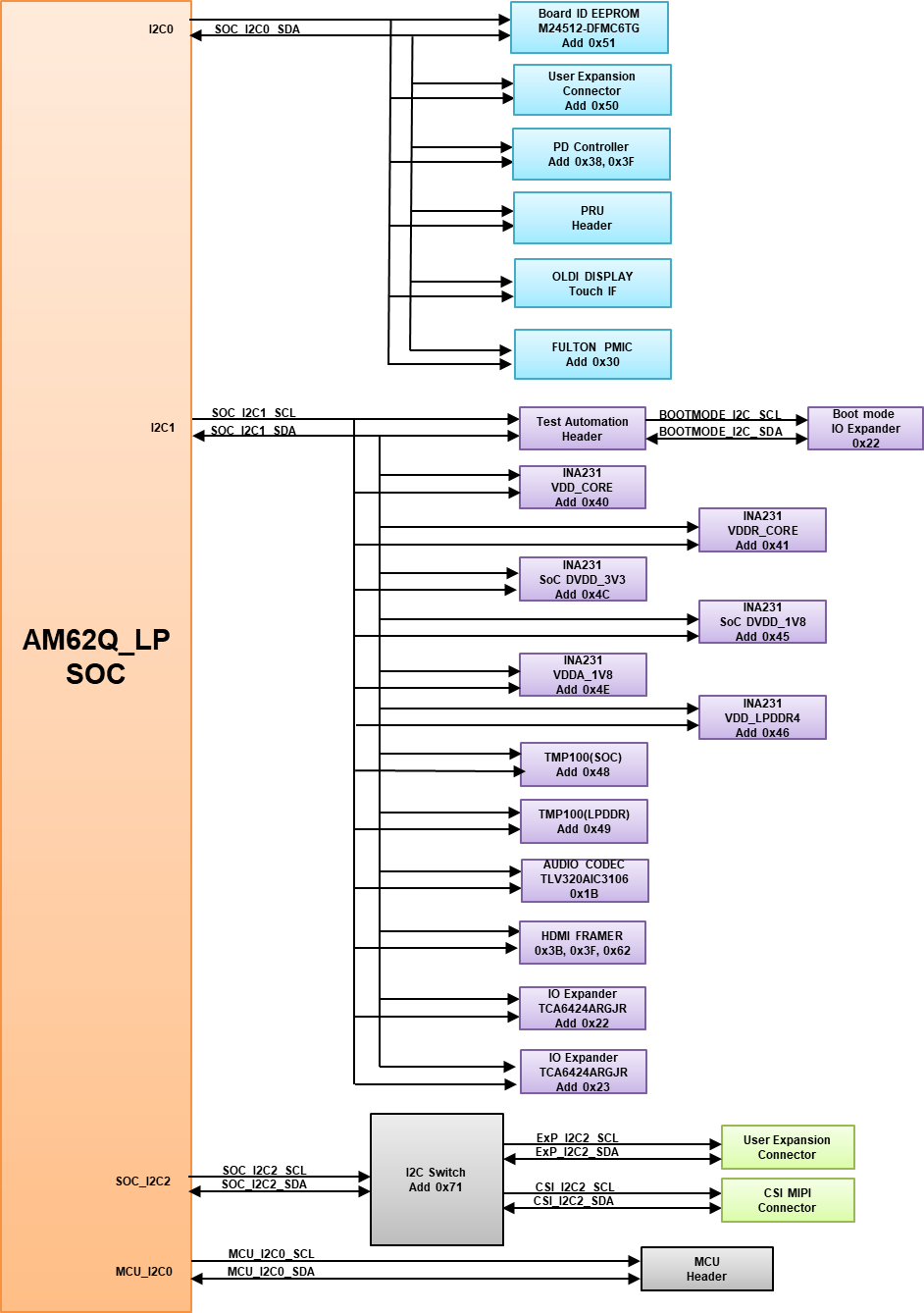

3.5.19 I2C Address Mapping

There are three I2C interfaces used in AM62x-Low Power SK EVM board.

- SoC_I2C0 Interface: SoC I2C [0] is connected to Board ID EEPROM, User Expansion Connector Header, USB PD controller, PRU header, PMIC and OLDI Display Touch interface.

- SOC I2C1 Interface: SoC I2C [1] is connected to Test Automation Header, Current Monitors, Temperature Sensors, Audio Codec, HDMI Transmitter, , GPIO Port Expander.

- SOC I2C2 Interface: Soc I2C [2] is Connected to the User Expansion Connector Header and CSI Camera Connector.

- MCU I2C0 Interface: MCU I2C [0] is Connected to MCU Header.

Figure 3-30 I2C Interface Block Diagram

Figure 3-30 I2C Interface Block DiagramTable 3-28 I2C Mapping Table

| I2C Port | Device/Function | Part# | I2C Address |

| SoC_I2C0 | Board ID EEPROM | M24512-DFMC6TG | 0x51 |

| SoC_I2C0 | User Expansion Connector | <connector interface> | |

| SoC_I2C0 | USB PD Controller | TPS65988DHRSHR | 0x38, 0x3F |

| SoC_I2C0 | PRU Header | <connector interface> | |

| SoC_I2C0 | OLDI Display Touch Interface | <connector interface> | |

| SoC_I2C1 | PMIC | TPS65219 | 0x30 |

| SoC_I2C1 | Test Automation Header | <connector interface> | |

| SoC_I2C1 | Current Monitors | INA231AIYFDR |

0x40, 0x41, 0x4C, 0x45, 0x4E & 0x46 |

| SoC_I2C1 | Temperature Sensors | TMP100NA/3K | 0x48, 0x49 |

| SoC_I2C1 | Audio Codec | TLV320AIC3106IRGZT | 0x1B |

| SoC_I2C1 | HDMI Transmitter | SiI9022ACNU | 0x3B, 0x3F, 0x62 |

| SoC_I2C1 | GPIO Port Expander | TCA6424ARGJR | 0x22, 0x23 |

| SoC_I2C2 | CSI Camera Connector | <connector interface> | |

| SoC_I2C2 | User Expansion Connector | <connector interface> | |

| MCU_I2C0 | MCU Header | <connector interface> | |

| Others | |||

| BOOTMODE_I2C | I2C Bootmode Buffer | TCA6424ARGJR | 0x22 |

| BOOTMODE_I2C | Test Automation Header | <connector interface> | |