SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

3.7.15.4 Power Supply

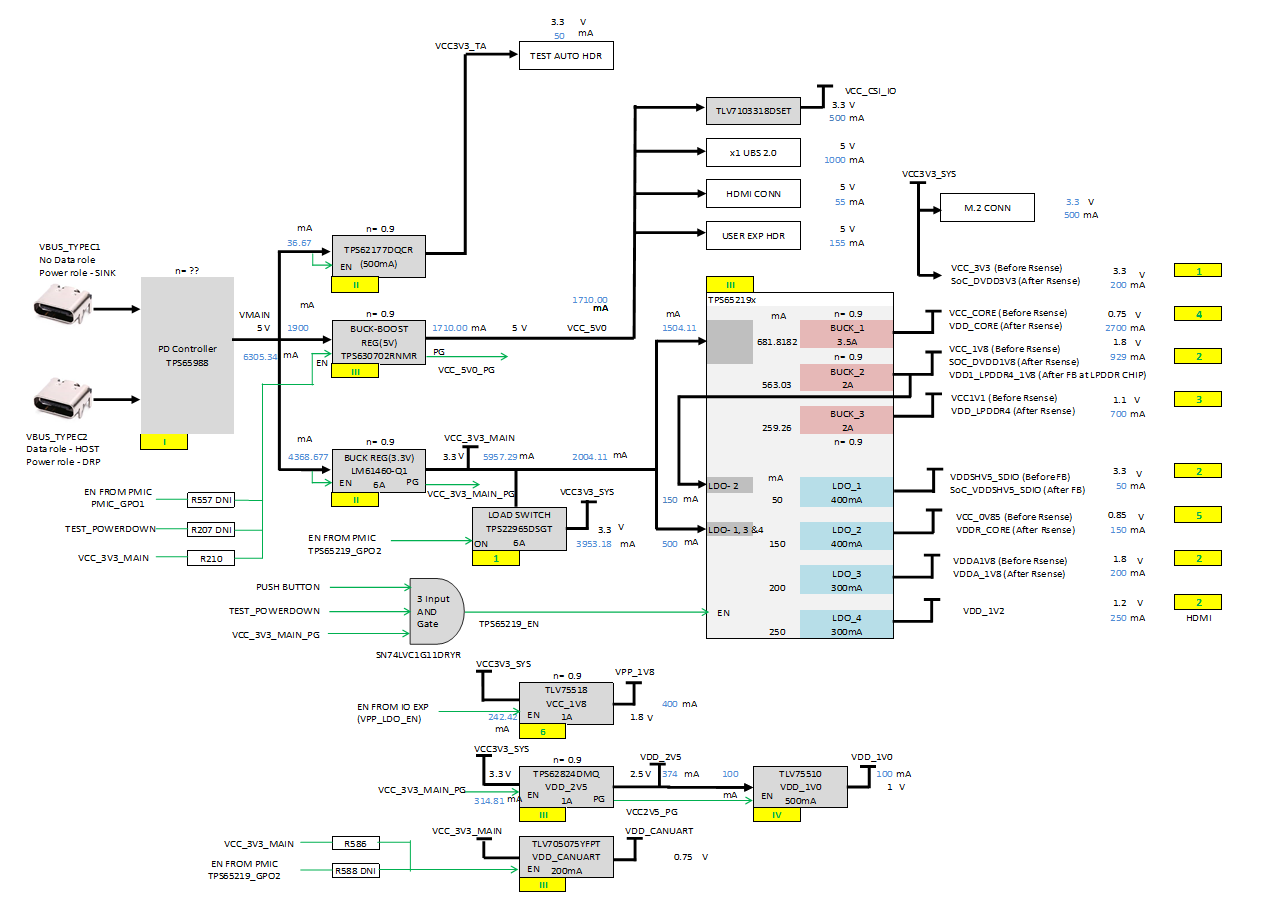

AM62x-Low Power SK EVM utilizes an array of DC-DC converters to supply the various memories, clocks, SoC and other components on the board with the necessary voltage and the power required.

The figure below shows the various discrete regulators and LDOs used to generate power rails and the current consumption of each peripheral on AM62x-Low Power SK EVM board.

Figure 3-26 Power Architecture

Figure 3-26 Power ArchitectureThe following sections describe the power distribution network topology that supplies the SK EVM board, supporting components and reference voltages.

The AM62x-Low Power SK EVM board includes a power solution based on a PMIC as well as discrete power supply components. The initial stage of the power supply will be VBUS voltage from either of the two USB Type C connectors J13 and J15. USB Type-C Dual PD controller of Mfr. Part# TPS65988DHRSHR is used for negotiation of the required power to the system.

Buck-Boost controller TPS630702RNMR and Buck converter LM61460-Q1 are used for the generation of 5V and 3.3V respectively and the input to the regulators is the PD output. These 3.3V and 5V are the primary voltages for the AM62x-Low Power SK EVM Board power resources. The 3.3V supply generated from the Buck regulator LM61460-Q1 is the input supply to the Various SOC regulators and LDOs. The 5V supply generated from the Buck Boost regulator TPS630702RNMR is used for powering the onboard peripherals. Discrete regulators and LDOs used on board are:

- TPS62824DMQR - To generate VDD_2V5 rail for PHY and DDR peripherals

- TLV75510PDQNR - To generate VDD_1V0 for Ethernet PHYs

- TPS65219 - To generate various SoC and peripheral supply’s

- TPS62177DQCR - Powering the always-on circuits of Test Automation Section

- TLV75518LDO - e-Fuse programming of SoC

- TPS79601LDO - XDS110 On board emulator

- TPS73533LDO - FT4232 UART to USB Bridge

- TLV705075YFPT- To generate VDD_CANUART rail

Additionally, GPIO from the test automation header is also connected to the TPS630702RNMR Enable pin to control ON/OFF of the SKEVM via the test automation board. It only disables the VCC_5V0 output of TPS630702RNMR from which all other power supplies are derived. SoC has different IO groups.