ZHCSO15A December 2021 – February 2023 DLPC4420

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 System Oscillators Timing Requirements

- 6.7 Test and Reset Timing Requirements

- 6.8 JTAG Interface: I/O Boundary Scan Application Timing Requirements

- 6.9 Port 1 Input Pixel Timing Requirements

- 6.10 Port 3 Input Pixel Interface (via GPIO) Timing Requirements

- 6.11 DMD LVDS Interface Timing Requirements

- 6.12 Synchronous Serial Port (SSP) Interface Timing Requirements

- 6.13 Programmable Output Clocks Switching Characteristics

- 6.14 Synchronous Serial Port Interface (SSP) Switching Characteristics

- 6.15 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

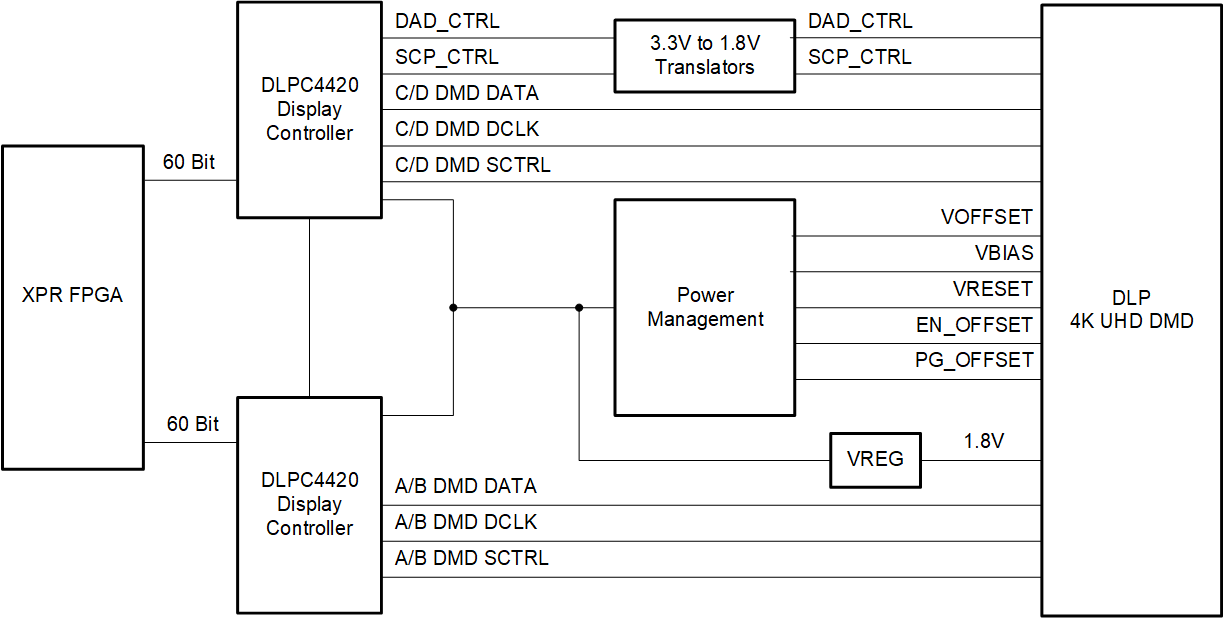

3 说明

DLPC4420 是用于 DLP® 显示芯片组的数字显示控制器。该芯片组包含 DLPC4420 显示控制器、DLP 数字微镜器件 (DMD)、DLPA100 控制器电源管理器件和 DLPA300 DMD 微镜驱动器(请参阅 DMD 数据表)。这款解决方案非常适合需要高分辨率、高亮度和系统简易性的显示系统。为了确保可靠运行,必须始终将 DLPC4420 显示控制器与 DLP DMD 和相应的 DLP 电源管理器件配合使用。

器件信息

| 器件型号(1) | 封装 | 封装尺寸(标称值) |

|---|---|---|

| DLPC4420 | ZPC (516) | 27.00mm × 27.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

简化版原理图

简化版原理图