ZHCUC00 May 2024

5.1.3.2 布局指南

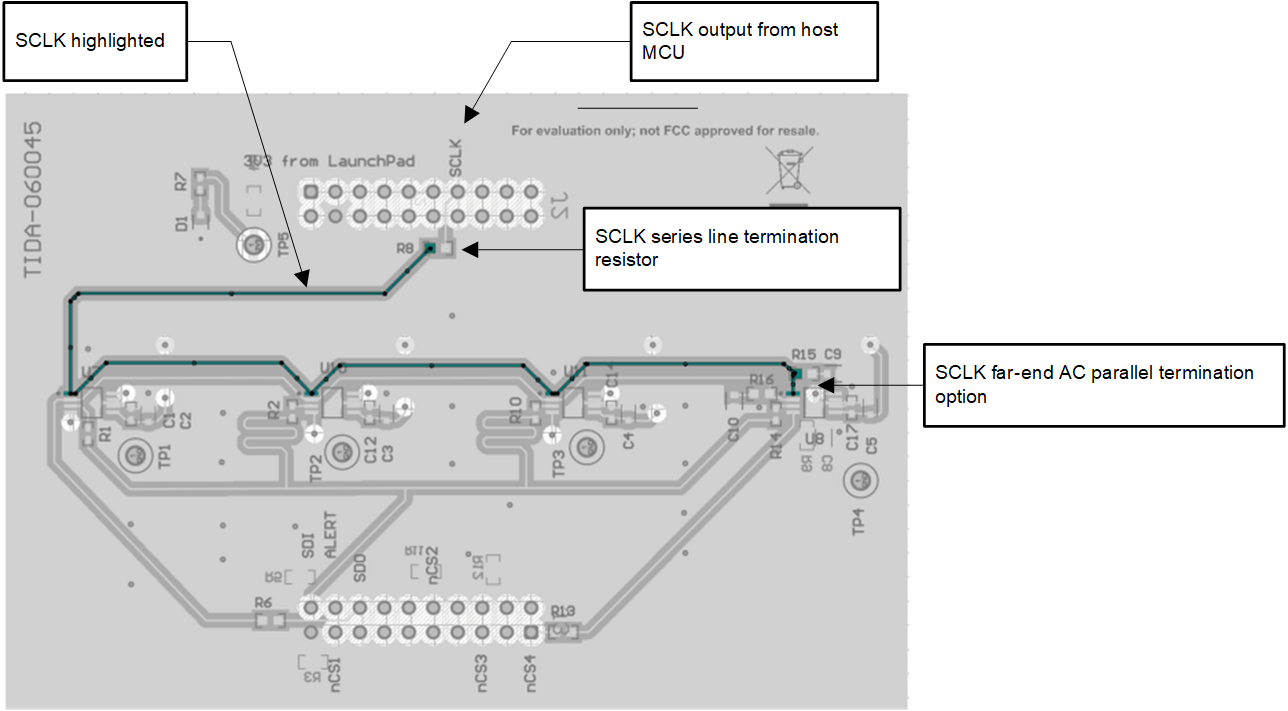

SPI 时钟信号 SCLK 的布局如图 5-1 所示。SCLK 布设在顶层,以菊花链形式从第一个 TMAG5170 (U7) 连接到最后一个 TMAG5170 (U8),带有串行线路端接电阻器和可选的远端交流并联端接。nALERT 和 MOSI (TMAG5170 SDI) 信号布线方式相同。下面的中间 1 层上的纯色 GND 平面用作返回 GND。

图 5-1 SPI 时钟 (SCLK) 布线

图 5-1 SPI 时钟 (SCLK) 布线每个 TMAG5170 的单独 SDO 输出 (SPI MISO) 都有一个串行线路端接电阻器。每个 TMAG5170 的四条 SDO 迹线以星型方式布线,长度相似,然后合并为单条迹线以连接到主机处理器 MISO 输入引脚。

图 5-2 MISO 长度相似的星型拓扑

图 5-2 MISO 长度相似的星型拓扑