ZHCACP5A september 2021 – may 2023 AFE7900 , AFE7901 , AFE7903 , AFE7920 , AFE7950 , AFE7950-SP , AFE7951 , AFE7953 , AFE7955 , AFE7958

2.1.1.1 ADC 至 DAC JESD 环回

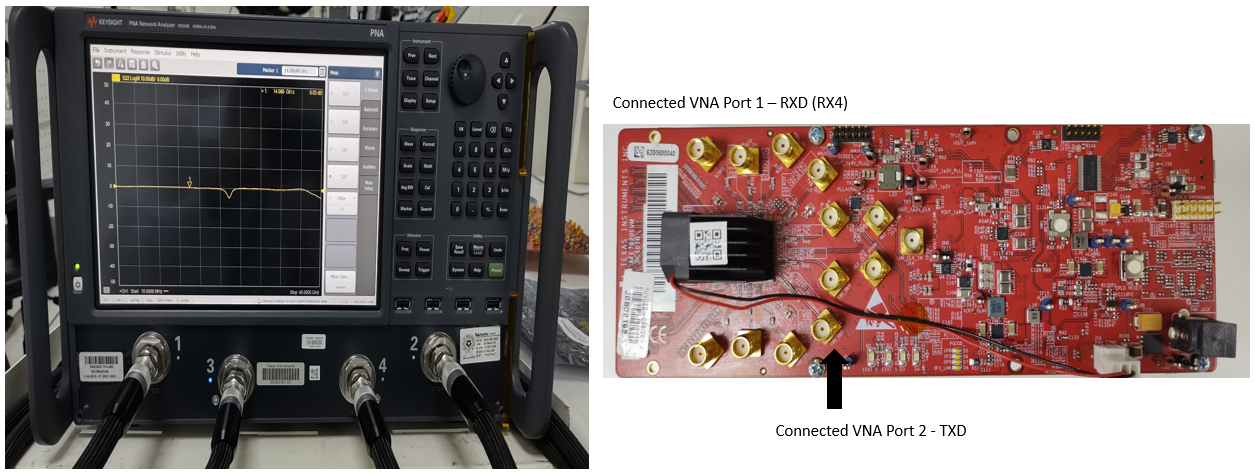

矢量网络分析器端口 1 连接到器件的 RXD 通道,而 TXD 通道重新连接到矢量网络分析器的端口 2,以捕获群延迟和环路增益。矢量网络分析器在内部扫描相对于 SERDES 数据速率设置的带宽。

图 2-1 硬件方框图 – JESD 环回

图 2-1 硬件方框图 – JESD 环回