ZHCACP5A september 2021 – may 2023 AFE7900 , AFE7901 , AFE7903 , AFE7920 , AFE7950 , AFE7950-SP , AFE7951 , AFE7953 , AFE7955 , AFE7958

2.1.2.1 ADC 至 DAC JESD 环回

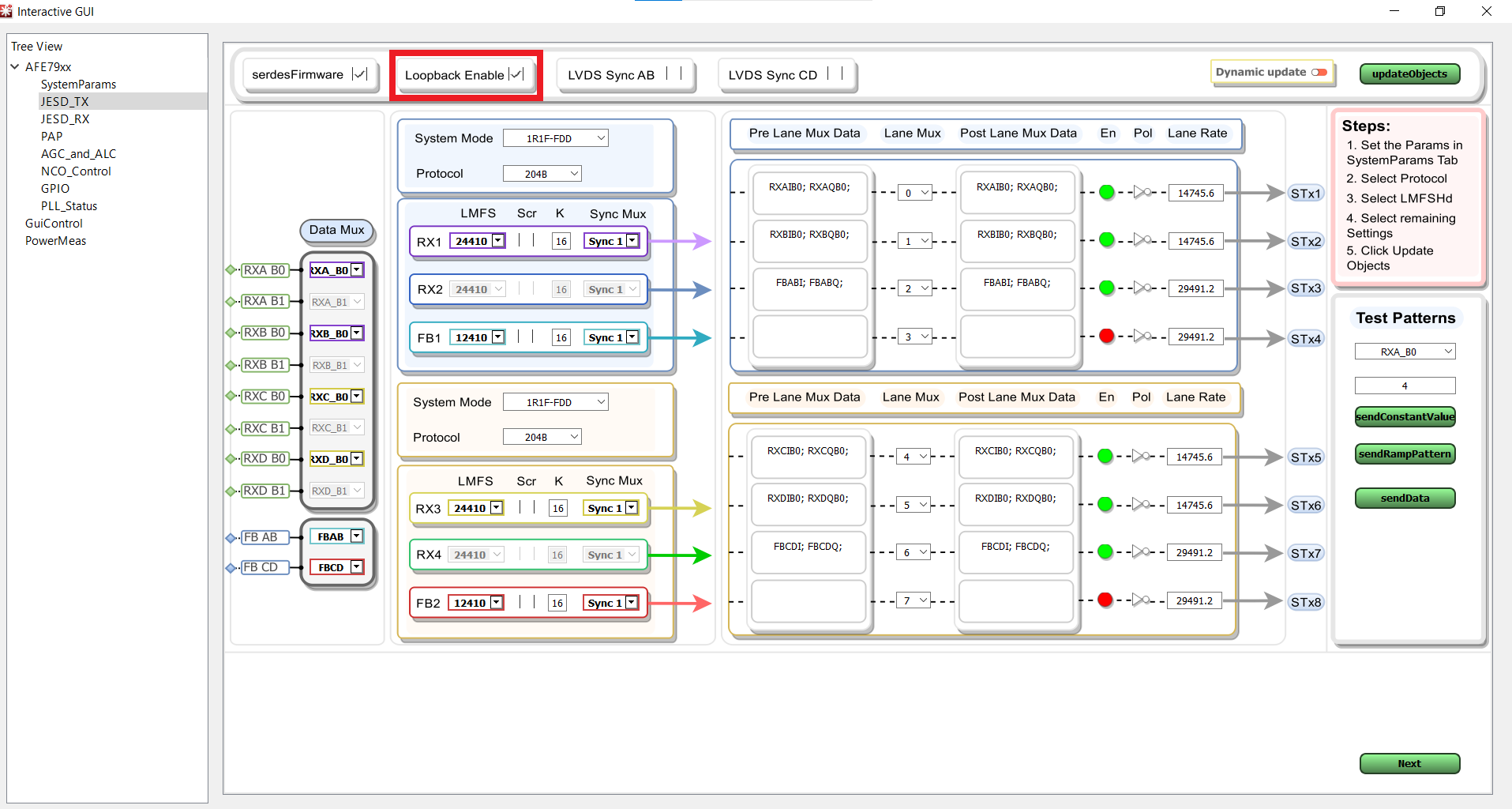

AFE 支持通过内部 JESD 块进行 RX ADC 至 DAC 环回。这可以通过将 jesdLoopBackEn 位设置为 True 来启用。以下是使用此功能时需要满足的条件。

- ADC 和 DAC 接口速率必须相同。

- RX 和 TX 的 JESD 设置和通道速率必须相同。

- RxA 必须环回到 TXA,RXB 必须环回到 TXB,依此类推。

- 环回模式使用如图 2-3 所示的复选框启用。

图 2-3 ADC 至 DAC JESD 环回使能模式

图 2-3 ADC 至 DAC JESD 环回使能模式