ZHCACP5A september 2021 – may 2023 AFE7900 , AFE7901 , AFE7903 , AFE7920 , AFE7950 , AFE7950-SP , AFE7951 , AFE7953 , AFE7955 , AFE7958

2.1.4.1.4 JESD 368.64MSPS

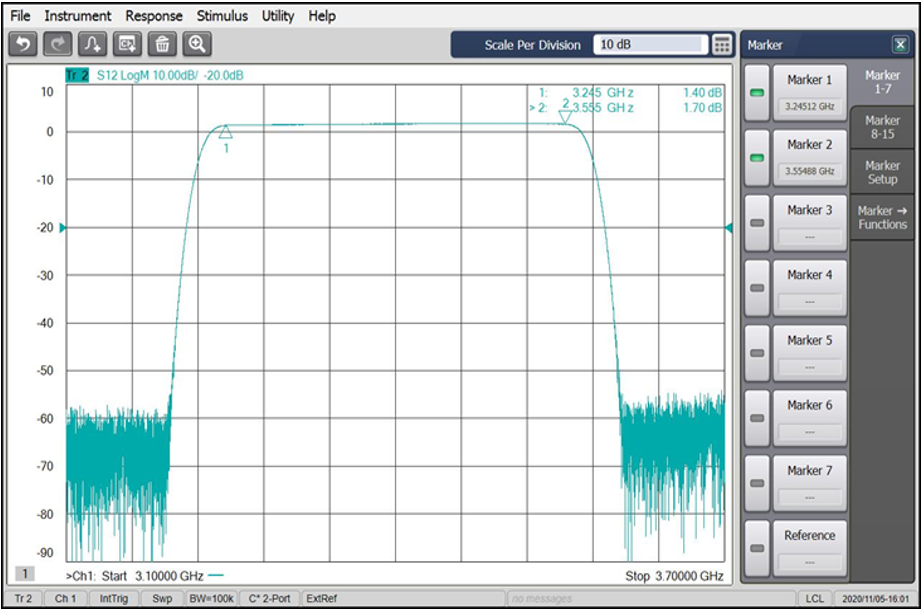

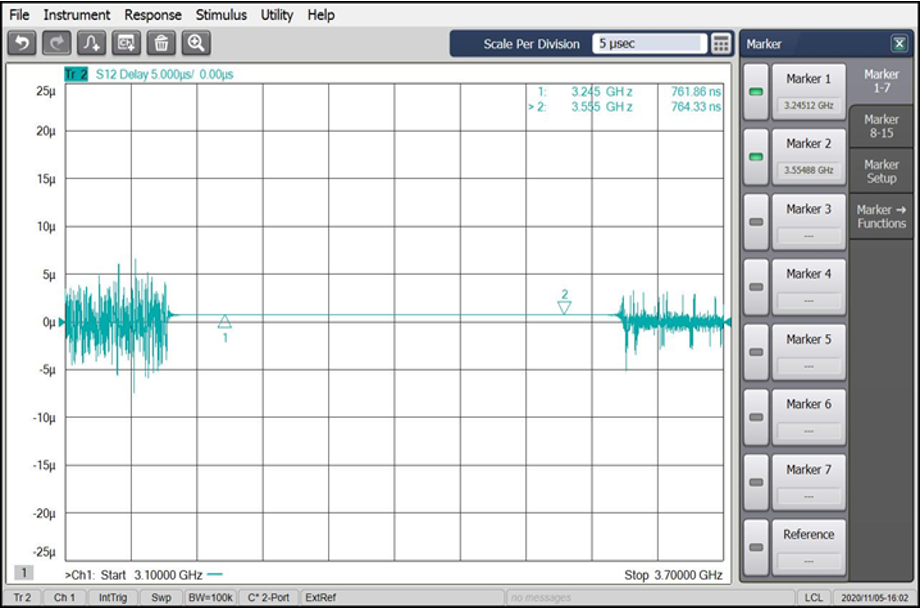

内部 JESD 设置为 368.64MSPS 的数据速率,以实现 350MHz 信号带宽。幅度响应在通带内无纹波,群延迟测量值为 760ns,器件无任何纹波演示线性相位响应。

图 2-10 幅度响应 368.64MSPS

图 2-10 幅度响应 368.64MSPS 图 2-11 群延迟 368.64MSPS

图 2-11 群延迟 368.64MSPS