ZHCACP5A september 2021 – may 2023 AFE7900 , AFE7901 , AFE7903 , AFE7920 , AFE7950 , AFE7950-SP , AFE7951 , AFE7953 , AFE7955 , AFE7958

2.1.4.2 ADC 至 DAC 低延迟环回

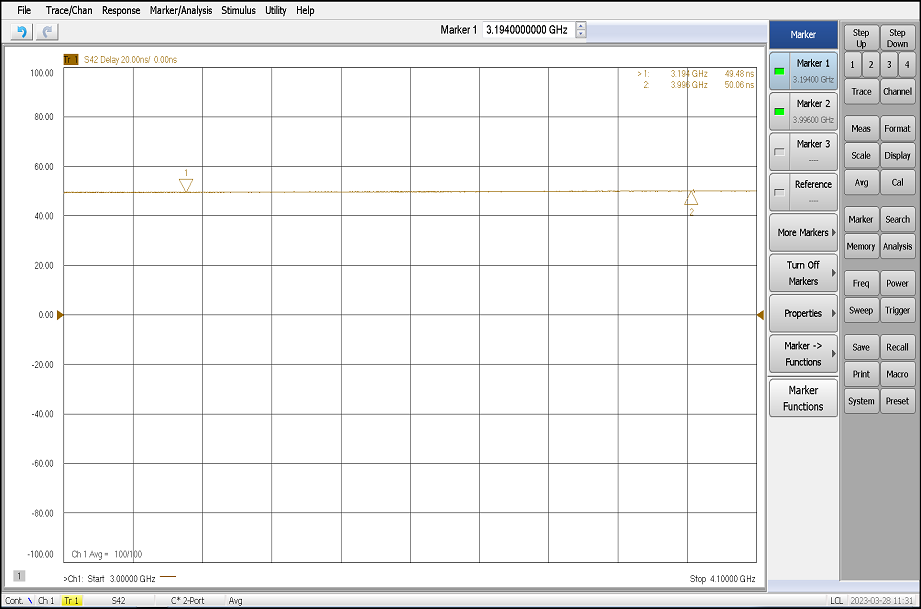

在此模式下,该器件在没有 DDC 和 JESD 接口的情况下进行了环回测试,实现了高模拟信号带宽(约 1GHz)。幅度响应不会反映通带中的任何衰减,该衰减更多是取决于外部匹配网络环路响应。群延迟测量值约为 49.48ns,展示了延迟最低的反馈信号链。

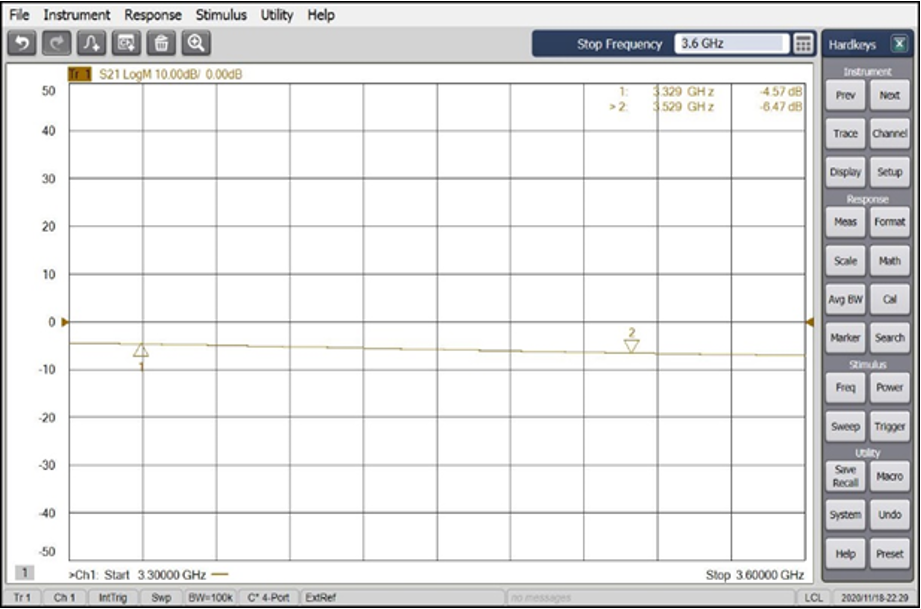

图 2-14 幅度响应 ADC 至 DAC 低延迟环回

图 2-14 幅度响应 ADC 至 DAC 低延迟环回 图 2-15 群延迟 ADC 至 DAC 低延迟环回

图 2-15 群延迟 ADC 至 DAC 低延迟环回有一个名为 lowLatencyModeProgDelay(afeInst, chNo, progDelay) 函数可用于改变此模式下的延迟值。此处,对于 FBAB,chNo 设置为 0,而对于 FBCD,则设置为 1。progDelay 的值可以在 0 到 23 之间变化,其中 0 对应于最小延迟。随着 progDelay 的值从 0 增加到 23,环路延迟会增加。