ZHCABQ7A May 2022 – June 2022 F28377D-SEP , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , UCD7138

2 SR 导通沿优化

图 2-1 显示了 C2000 和 UCD7138 的系统图。通常,数字控制方案将使 SR 导通沿与初级侧 PWM 一致,并进一步将上升沿延迟增加到 SR PWM 信号中。然而,由于体二极管导通时间较长,固定延迟或大于所需上升沿延迟无法提供最佳效率。实际上,使用 UCD7138 可以在CTRL 引脚悬空或连接至逻辑高电平 (3.3V)的情况下从本质上优化导通沿。

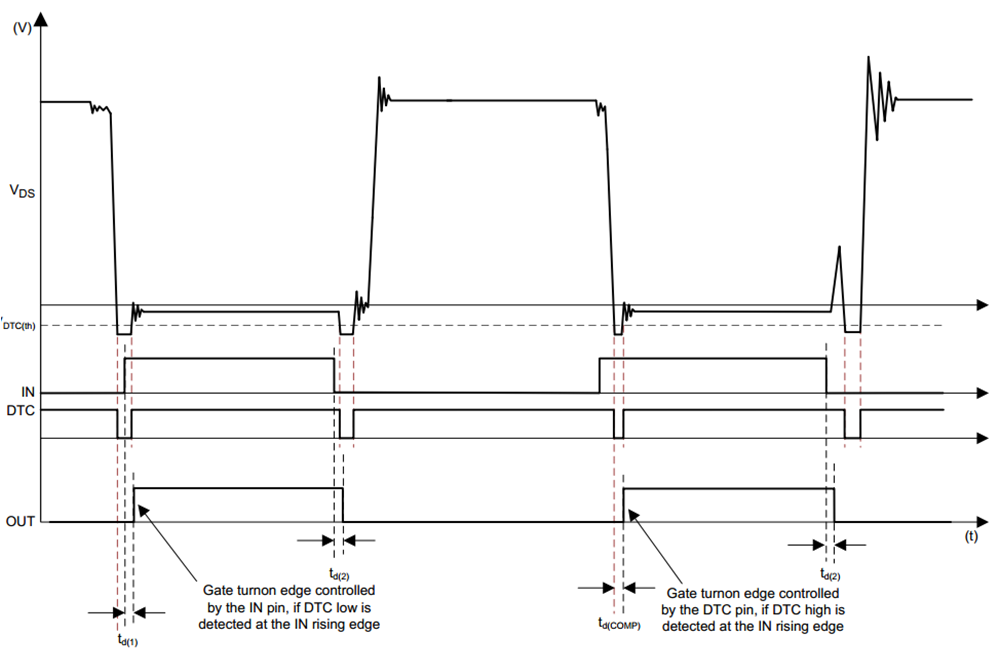

图 2-2 显示了使用 UCD7138 的导通沿优化方案。IN 是数字控制器(如 C2000)的栅极驱动器输入命令信号,OUT 是 SR 栅极驱动器输出信号。DTC 引脚是体二极管导通检测器输出,当 SR MOSFET 的体二极管导通时,DTC 引脚为低电平。

实际的栅极导通时序同时由数字控制器输出 IN 和 DTC 控制。只有当 IN 为高电平时,才可以开启 OUT。如果 DTC 在 IN 上升沿已经为低电平,应立即开启栅极驱动器输出;如果 DTC 在 IN 上升沿仍为高电平,则在到达 DTC 下降沿后立即开启栅极驱动器输出。然而,栅极关断沿仅由 IN 决定。栅极在 IN 下降沿立即被关闭。

因此,为了确保自由优化导通沿,用户只需将 IN 的上升沿设置为与带 C2000 的初级侧 PWM 相同。

图 2-2 导通沿优化

图 2-2 导通沿优化