ZHCABQ7A May 2022 – June 2022 F28377D-SEP , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , UCD7138

4 负电流检测和防范

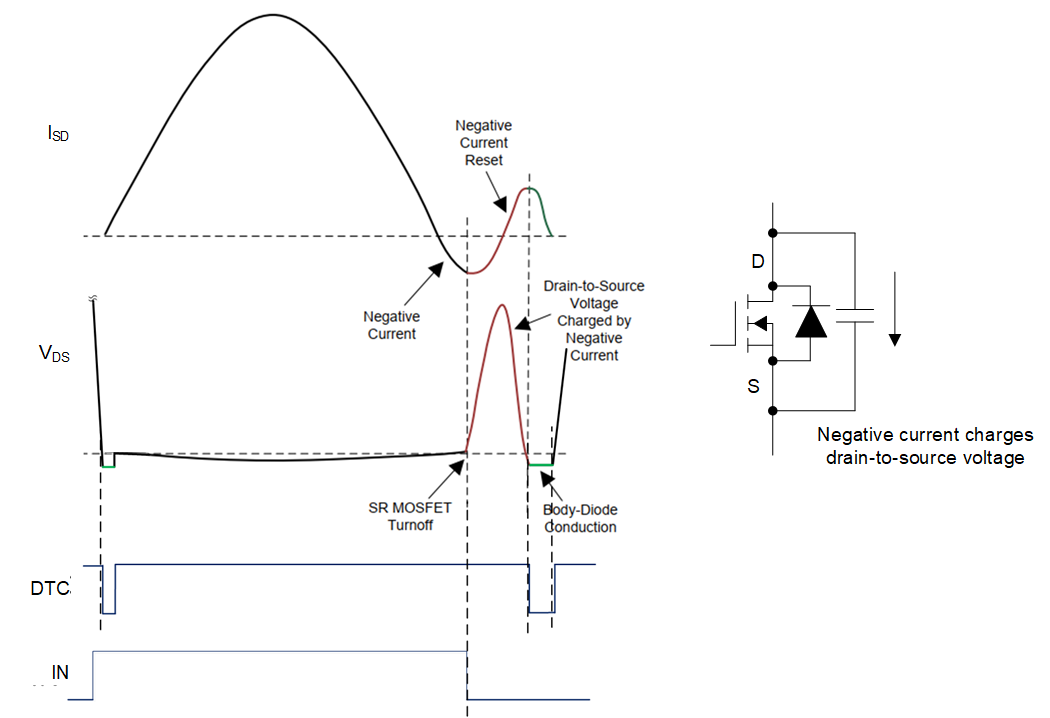

在正常运行过程中,SR 控制应始终与 LLC 转换器的初级侧 PWM 信号保持一致。然而,在大负载或线路瞬态运行过程中,LLC 转换器的开关频率会迅速变化。由于初级谐振电流和 SR 电流之间的响应差异,可能会高度引发 SR MOSFET 开启时间过长,从而在 SR MOSFET 上产生较大的负电流和较高的 Vds 尖峰。如图 4-1 所示,当出现负电流时,负电流会为 SR MOSFET 漏源电容充电,异常的 Vds 过应力可能会对 SR MOSFET 造成威胁。

图 4-1 SR 漏源电压迅速上升

图 4-1 SR 漏源电压迅速上升在先前技术中, UCD3183A 控制器具有专用接口来处理 DTC 信号,以防范负电流问题 4。在 DTC 检测窗口内(如图 3-1 所示),如果未检测到 DTC 低电平时间或此时间非常短暂,就意味着 SR 关闭过迟。UCD3138A 计算当前周期的体二极管导通时间,并在下一周期调整 SR 导通时间。当检测窗口内检测到的体二极管导通时间小于某一阈值时,UCD3138A 会将它作为故障处理,并将 SR 导通时间缩短一个较大的预编程值。

虽然 C2000 器件并不为 UCD7138 提供 DTC 接口,但应用报告讨论了如何使用 CLB 实施与 UCD7138 相似的负电流预防方案。在正常工作期间,确保体二极管短时间导通是安全的,因此在图 3-1 中的检测窗口内将不会发生 DTC 高电平事件,而如果关闭 SR 过迟,DTC 将在输入下降沿后的一段时间内保持高电平。因此,可以计算 DTC 高电平的持续时间来检测负电流事件。

以下步骤显示了如何利用 CLB 模块尽快检测并防止负电流。

- 定义 CLB 计数器的检测窗口,因为只需要检测 IN

信号的下降沿和 DTC 信号的上升沿之间的高电平事件。有限状态机 (FSM) 模块用于创建检测窗口,其中 E0 是指 IN 的下降沿,而 E1 是指 DTC

的上升沿,如图 4-2 所示。S0 的 FSM 公式可以推导为 Equation1.

因此,S0 用作计数器 0 的“RESET”(复位)输入,这意味着 CLB 计数器将在检测窗口外复位为 0。

图 4-2 FSW 模块中的状态机 - 然后,将原始 DTC 信号设置为计数器的 MODE_0 输入,以便采集 DTC 高电平时间。

- 如果采集的 DTC 高电平时间大于阈值,则通过 HLC 产生 CLB ISR,指示存在负电流事件,然后在下一周期将 SR 导通时间减少一个较大的预编程值。请注意,建议以最高优先级设置 CLB ISR,以保证系统的高可靠性。

图 4-3 显示了完成的 CLB 逻辑块配置方框图,包括Topic Link Label3 中的谐振回路元件补偿方案和负电流检测方案。CLB ISR 由计数器 0 MATCH1 事件触发,其中 MATCH1 被设置为负检测阈值,例如 5 代表 50ns。此外,S0 还用于在 S0 上升沿(也就是 SR 周期结束时)触发 HLC,将计数器 1 的计数器值从 CLB 移至 CPU,以达到调整 SR 钳位导通时间的目的。

以下代码片段提供了一个示例,演示了如何处理 CLB ISR 中的负电流事件,其中 negative_current_flag 用于指示 SR PWM 寄存器将因负电流事件而临时改变,并且需要稍后恢复为预期值。

__interrupt void clb1ISR(void) { negative_current_flag =

1; EPWM2_CMPA = EPWM2_CMPA-reduce_step; }