ZHCABI1B February 2022 – January 2024 AM2434 , AM6411 , AM6412 , AM6421 , AM6441 , AM6442

4.4.1 测试设置

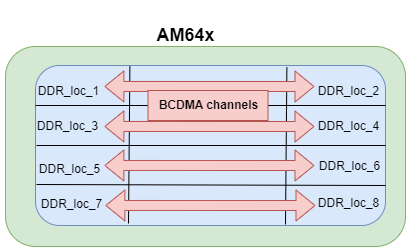

本节介绍了使用 UDMA 为 DDR 到 DDR 复制执行基准测试所用的测试设置。

图 4-5 AM64x DDR 至 DDR 数据流

图 4-5 AM64x DDR 至 DDR 数据流例如:

DDR_loc_1 = 0xA0000000 + 0x00000000U

DDR_loc_2 = 0xA0000000 + 0x01000000U

DDR_loc_3 = 0xA0000000 + 0x02000000U

DDR_loc_4 = 0xA0000000 + 0x03000000U

以此类推。